Transcription

SRAM DesignMemory

Chapter Overview Memory Classification Memory Architectures The Memory Core Periphery ReliabilityMemory

Semiconductor MProgrammable (PROM)FLASHShift RegisterCAMMemory

Memory Architecture: DecodersM bitsN WordsS1S2SN-2SN 1S0Word 0Word 1Word 2StorageCellWord 1A1Word 2AK -1Word N-2Word 0A0DecoderS0M bitsWord N-2Word N-1Word N-1Input-Output(M bits)Input-Output(M bits)N words N select signalsToo many select signalsMemoryStorageCellDecoder reduces # of select signalsK log2N

Array-Structured Memory ArchitectureProblem: ASPECT RATIO or HEIGHT WIDTHAKAK 1AL-1Bit LineRow Decoder2L-KStorage CellWord LineM.2KSense Amplifiers / DriversA0AK -1Column DecoderInput-Output(M bits)MemoryAmplify swing torail-to-rail amplitudeSelects appropriateword

Hierarchical Memory bal Data BusControlCircuitryBlock SelectorGlobalAmplifier/DriverI/OAdvantages:1. Shorter wires within blocks2. Block address activates only 1 block power savingsMemory

Memory Timing: DefinitionsRead CycleREADRead AccessRead AccessWrite CycleWRITEWrite AccessData ValidDATAData WrittenMemory

Memory Timing: ApproachesMSBAddressBusLSBRow Address Column AddressAddressBusRASAddressAddress transitioninitiates memory operationCASRAS-CAS timingDRAM TimingMultiplexed AdressingMemorySRAM TimingSelf-timed

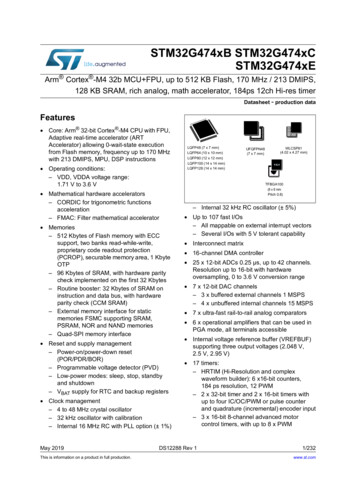

Read-Write Memories (RAM) STATIC (SRAM)Data stored as long as supply is appliedLarge (6 transistors/cell)FastDifferential DYNAMIC (DRAM)Periodic refresh requiredSmall (1-3 transistors/cell)SlowerSingle EndedMemory

6-transistor CMOS SRAM CellWLVDDM2M4QM6QM5M1M3BLBLMemory

CMOS SRAM Analysis (Write)WLVDDM4Q 0Q 1M5M6M1VDDBL 1BL 022V DD V DDV DD V DD- k p, M4 ( V DD – V Tp ) ----------- – ---------- k n, M6 ( V DD – V Tn ) ----------- – ---------22 8 8 2V DD VDDkn, M5 VDDV DD 2- kn M1 ( VDD – V Tn )---------- – ----------- ------------- ----------- – VTn ---------,2 22 2 8 Memory(W/L)n,M6 0.33 (W/L)p,M4(W/L)n,M5 10 (W/L)n,M1

CMOS SRAM Analysis (Read)WLVDDM4BLQ 0M6M5V DDBLQ 1M1VDDV DDCbitC bitVDD V 2kn, M5 VVD D 2DDD D --------------- ----------- – VTn ------------ kn, M1 ( VD D – V Tn ) ------------ – ---------- 2 2 228 (W/L)n,M5 10 (W/L)n,M1(supercedes read constraint)Memory

6T-SRAM — LayoutVDDM2M4QQM1M3GNDM5M6BLMemoryBLWL

Resistance-load SRAM CellWLVDDRLM3BLQRLQM1M2M4BLStatic power dissipation -- Want RL largeBit lines precharged to VDD to address t p problemMemory

Periphery Decoders Sense Amplifiers Input/Output Buffers Control / Timing CircuitryMemory

Row DecodersCollection of 2M complex logic gatesOrganized in regular and dense fashion(N)AND DecoderNOR DecoderMemory

Dynamic DecodersPrecharge devicesGNDGNDVDDWL 3VDDWL 2VDDWL 1WL 3WL 2WL 1VDDWL 0V DD φA0A0A1A1Dynamic 2-to-4 NOR decoderWL 0A0A0A1A1φ2-to-4 MOS dynamic NAND DecoderPropagation delay is primary concernMemory

A NAND decoder using 2-input predecodersWL 1WL 0A0A1 A0 A1 A0 A1 A0A 1A 2A3 A2 A3 A2 A3 A2 A3A1 A 0A3 A2A0A1A2A3Splitting decoder into two or more logic layersproduces a faster and cheaper implementationMemory

4 input pass-transistor based columndecoderA0A12 input NOR decoderBL0BL1BL2BL3S0S1S2S3Ddvantage: speed (tpd does not add to overall memory access time)only 1 extra transistor in signal pathsadvantage: large transistor countMemory

4-to-1 tree based column decoderBL0BL1BL2BL3A0A0A1A1DNumber of devices drastically reducedDelay increases quadratically with # of sections; prohibitive for large decodersSolutions: buffersprogressive sizingcombination of tree and pass transistor approachesMemory

Decoder for circular �φ.RφφRφVDDMemoryφRφφ

Sense Amplifierstmake V as smallas possibleC V ---------------pIavlargesmallIdea: Use Sense Amplifersmalltransitions.a.inputMemoryoutput

Differential Sensing - SRAMVDDV DDBLPCVDDEQVDDy M3BLWLiM4M1xSEM2yx xxM5SE(b) Doubled-ended Current Mirror AmplifierVDDSRAM cell iyDiff.SensexxAmpyyDDyxxSE(a) SRAM sensing scheme.(c) Cross-Coupled AmplifierMemory

Latch-Based Sense AmplifierEQBLBLVDDSESEInitialized in its meta-stable point with EQOnce adequate voltage gap created, sense amp enabled with SEPositive feedback quickly forces output to a stable operating point.Memory

Single-to-Differential ConversionWLBLx Diff.x S.A.cellyyHow to make good Vref?MemoryVref

Address Transition yATD

Reliability and YieldMemory

Open Bit-line Architecture —Cross CAmplifierMemoryCBLCCC

Folded-Bitline ArchitectureWL1BL.BLWL1WLDWL0 WL0CWBLWLDCBLCyxCCCCCSenseEQ AmplifierxCBLCWBLMemoryy

Transposed-Bitline ArchitectureBL’CcrossBLSABLBL"(a) Straightforward bitline routing.BL’BLCcrossSABLBL"(b) Transposed bitline architecture.Memory

Alpha-particlesα-particleWLVDDBLSiO2n 1 particle 1 million carriersMemory

YieldYield curves at different stages of process maturity(from [Veendrick92])Memory

n DecoderMemoryRow DecoderRedundantcolumnsColumnAddressFuseBank

Semiconductor Memory TrendsMemory Size as a function of time: x 4 every three yearsMemory

Semiconductor Memory TrendsIncreasing die sizefactor 1.5 per generationCombined with reducing cell sizefactor 2.6 per generationMemory

Semiconductor Memory TrendsTechnology feature size for different SRAM generationsMemory

Memory Chapter Overview Memory Classification Memory Architectures The Memory Core Periphery Reliability. Memory Semiconductor Memory Classification RWM NVRWM ROM EPROM E2PROM FLASH Random Access Non-Random Access SRAM DRAM Mask-Programmed Programmable (PROM) FIFO Shift Register CAM LIFO. Memory Memory Architecture: Decoders Word 0 Word 1 Word 2 Word N-1 Word N-2 Input .