Transcription

Computer Systems and NetworksìECPE 170 – Jeff Shafer – University of the PacificMIPS Assembly(Arithmetic, Branches)

2Lab ScheduleActivitiesì This WeekìTuesday: MIPS lecture(arithmetic, branches)ìThursday: MIPS lecture(memory)Assignments Dueì Lab 10ìDue by Apr 8th 5:00amì Lab 11ìDue by Apr 16th 5:00amì Lab 12ìComputer Systems and NetworksDue by Apr 28th 5:00amSpring 2021

3Person of the Day – John Cockeì Computer architecture pioneerì“Father of RISC Architecture”ìDeveloped IBM 801 processor,1975-1980ì Winner, ACM Turing Award, 1987RISC Reduced Instruction Set ComputingAchieve higher performance with simpleinstructions that execute fasterComputer Systems and NetworksSpring 2021

4Person of the Day – John Hennessyì Computer architecture pioneerì Popularized RISC architecture in early1980’sì Founder of MIPS Computer Systemsin 1984ì Past president of Stanford UniversityComputer Systems and NetworksSpring 2021

5Class to DateHumanCompilerCompilerLinker(C Code)(Assemblycode)(Object file /binary code)(Executableprogram)Computer Systems and NetworksSpring 2021

6Class NowHumanAssemblerLinker(Assemblycode)(Object file /binary code)(ExecutableProgram)Computer Systems and NetworksSpring 2021

7MIPSComputer Systems and NetworksìSpring 2021

8MIPS Overviewì Family of computer processors first introduced in1981ì Microprocessor without Interlocked Pipeline Stagesì Original acronymì Now MIPS stands for nothing at all Computer Systems and NetworksSpring 2021

9MIPS Productsì Embedded devicesì Cisco/Linksys routersì Cable boxesì MIPS processor is buried inside System-on-a-Chip (SOC)ì Gaming / entertainmentì Nintendo 64ì Playstation, Playstation 2, PSPì Computers?ì Not so much anymore ì SGI / DEC / NEC workstations back in 1990’sComputer Systems and NetworksSpring 2021

10MIPS Productsì NASA New Horizons probeìLaunched January 2006ì MIPS “Mongoose-V” chipì12 MhZìRadiation HardenedìBased on R3000(PlayStationCPU)(2006, pdfComputer Systems and NetworksSpring 2021

11MIPS Designì RISC – What does this mean?ì Reduced Instruction Set Computingì Simplified design for instructionsì Use more instructions to accomplish same taskì But each instruction runs much faster!ì 32 bits (originally) – What does this mean?ì 1 “word” 32 bitsì Size of data processed by an integer add instructionì New(er) MIPS64 design is 64 bits, but we won’tfocus on thatComputer Systems and NetworksSpring 2021

12MIPS Assembly ProgrammingComputer Systems and NetworksìSpring 2021

13Quotes – Donald Knuth“People who are more thancasually interested incomputers should have at leastsome idea of what theunderlying hardware is like.Otherwise the programs theywrite will be pretty weird.”– Donald KnuthThis is your motivation in the assembly labs!Computer Systems and NetworksSpring 2021

14Why Learn Assembly Programming?ì Computer Science trackì Understand capabilities (and limitations) of physicalmachineì Ability to optimize program performance (orfunctionality) at the assembly level if necessaryì Computer Engineer trackì Future courses (e.g. ECPE 173) will focus on processordesignì Start at the assembly programming level and move intohardwareì How does the processor implement the add instruction?ì How does the processor know what data to process?Computer Systems and NetworksSpring 2021

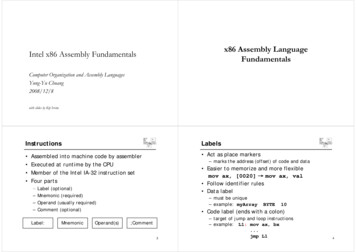

15Instruction Set Architectureì Instruction Set Architecture (ISA) is the interfacebetween hardware and softwareì Specifies the format of processor instructionsì Specifies the format of memory addresses(and addressing modes)ì Specifies the primitive operations the processor canperformComputer Systems and NetworksSpring 2021

16Instruction Set Architectureì ISA is the “contract” between the hardwaredesigner and the assembly-level programmerì Documented in a manual that can be hundreds orthousands of pages longì Example: Intel 64 and IA-32 Architectures SoftwareDevelopers Manualì architectures-software-developer-manuals.htmlì No joke – the manual PDF (combined volumes)from Nov 2020 is 5066 pages long!Computer Systems and NetworksSpring 2021

17Instruction Set Architectureì Processor families share the same ISAì Example ISAs:ì Intel x86ì Intel / AMD x86-64ì Intel Itaniumì ARMì IBM PowerPCì MIPSComputer Systems and NetworksAll completely different,in the way that C , Java,Perl, and PHP are alldifferent and yet learning onelanguage makes learningthe next one much easierSpring 2021

18Why MIPS?ì Why choose MIPS?ì The MIPS ISA manual (volume 1, at least) is a svelte108 pages!ì Extremely common ISA in textbooksì Freely available simulatorì Common embedded processorì Good building-block for other RISC-style processorsì Aligns with ECPE 173 courseComputer Systems and NetworksSpring 2021

19Arithmetic Instructionsì Additionadd result , input1 , input2 ì Subtractionsub result , input1 , input2 Operation / “Op code”Computer Systems and NetworksOperandsSpring 2021

20Task : Write Codeì Write MIPS assembly forf (g h) – (i j)add temp0, g, hadd temp1, i, jsub f, temp0, temp1Computer Systems and NetworksSpring 2021

21Congratulations!You’re now an assemblyprogramming expert!Computer Systems and NetworksSpring 2021

22Data Sourcesì Previous example was (just a little bit) fake ì We made up some variables:temp0, temp1, f, g, h, i, and jì This is what you do when programming in C (or any high level language)Problem: You can’t make upvariables in assembly!(as least, not in this fashion)Computer Systems and NetworksSpring 2021

23Data SourcesWhere can we explicitly place data in assembly programming?1.CPUALUCacheìOn the CPU itselfìVery close to ALUìTinyAccess time: 1 cycleìMemory2.Computer Systems and NetworksRegistersMemoryìOff-chipìLargeìAccess time: 100 cyclesSpring 2021

24Aside – Cacheì Review: Does the programmer explicitly managethe cache?ì Answer: No!ì The assembly programmer just reads/writesmemory addressesì Cache is managed automatically in hardwareì Result: Memory appears to be faster than it really isComputer Systems and NetworksSpring 2021

25ECPE 71ì From your knowledge of ECPE 71(Digital Design), how would youconstruct a register?Flip Flops! (D Flip Flop shown)Computer Systems and NetworksSpring 2021

26ECPE 71 – Group of RegistersComputer Systems and NetworksSpring 2021

27Registersì MIPS design: 32 integer registers, each holding 32 bitsì “Word size” 32 bitsNameUse zeroConstant value: ZERO s0- s7Local variables t0- t9Temporary resultsì This is only 19 – where are the rest of the 32?ì Reserved by convention for other usesì We’ll learn a few more later Computer Systems and NetworksSpring 2021

28Problem 1: Write Codeì Write MIPS assembly using registers for:f (g h) – (i j)Map: s0 g s1 h s2 i s3 j s4 fCode:add t0, s0, s1add t1, s2, s3sub s4, t0, t1P1Computer Systems and NetworksSpring 2021

29More Arithmetic Instructionsì Add Immediateaddi result , input1 , constant RegisterComputer Systems and NetworksRegisterCan be a positive ornegative number!Spring 2021

30Code Exampleì Write MIPS assembly using registers for:f g 20Map: s0 f s1 gComputer Systems and NetworksCode:addi s0, s1, 20Spring 2021

31MIPS Branches / LoopsComputer Systems and NetworksìSpring 2021

32Branchesì Branch on Equal (if 1 2, goto dest)beq reg1 , reg2 , destination ì Branch on Not Equal (if 1 ! 2, goto dest)bne reg1 , reg2 , destination ì Branch on Greater Than (if 1 2, goto dest)bgt reg1 , reg2 , destination Computer Systems and NetworksSpring 2021

33BranchesìBranch on Greater Than or Equal (if 1 2, goto dest)bge reg1 , reg2 , destination ì Branch on Less Than (if 1 2, goto dest)blt reg1 , reg2 , destination ìBranch on Less Than or Equal (if 1 2, goto dest)ble reg1 , reg2 , destination Computer Systems and NetworksSpring 2021

34Tests, Jumpì Set on Less Than (if 2 3, set 1 1, otherwise 0)slt reg1 , reg2 , reg3 ì Jump (goto dest)j destination Computer Systems and NetworksSpring 2021

35Code Exampleì Write MIPS assembly for:if (A B){ equal-code }else{ not-equal-code } after-if-code Computer Systems and NetworksTrue A B?False Spring 2021

36Code Exampleì Write MIPS assembly:Code:Map: s0 A s1 Bequal:done:Computer Systems and Networksbeq s0, s1,equal not-equal-code j done equal-code j done after-if-code Spring 2021

37Problem 2: Write Codeì Write MIPS assembly for:Map: s0 C s1 A s2 Bif( (A B) A 6 )C A;elseC B-A;P2Computer Systems and NetworksSpring 2021

38Code Exampleì Write MIPS assembly for:while (A ! B){ loop-body }FalseA! B?True post-loop-code Computer Systems and NetworksSpring 2021

39Code Exampleì Write MIPS assembly:Map: s0 A s1 BCode:start:done:Computer Systems and Networksbeq s0, s1,done loop-body j start post-loop-code Spring 2021

40Problem 3: Write Codeì Write MIPS assembly for:Map: s0 sum t0 isum 0;for(i 0; i 10; i ){sum i;}P3Computer Systems and NetworksSpring 2021

41Problem 4: Write Codeì Write MIPS assembly for:Map: s0 sum s1 i s2 jComputer Systems and Networkssum 0;for(i 0;i 10;i ){j i;while(j 2*i){sum sum j;j ;}}P4Spring 2021

42Problem 5: Write Codeì Write MIPS assembly for:Map: s0 sum s1 iwhile(1){sum sum i;i--;if(i 0)break;elsecontinue;}P5Computer Systems and NetworksSpring 2021

43Demos and ResourcesComputer Systems and NetworksìSpring 2021

44Demos1. QtSPIM is a MIPS simulator1. Review installation tutorial2. Walkthrough of simulator with example1.asmComputer Systems and NetworksSpring 2021

45Single StepButton!(Advance by 1 instruction)Computer Systems and NetworksSpring 2021

46Resourcesì Many resources available on ECS website1. The MIPS Example Programs page(basic arithmetic, looping, I/O, and function calls)1.The example1.asm program – Good example ofempty “stub program” template to use2. The MIPS Instruction Set page1. Partial guideComputer Systems and NetworksSpring 2021

47Resourcesì Files available in Canvas site (under ECPE 170)ì HP AppA.pdfì Appendix A from famous Hennessy & PattersonComputer Organization textbookì Assemblers, Linkers, and the SPIM simulatorì Starting on page 51 is an overview of the MIPSassembly commands!ì MIPS Green Sheet.pdfì “Cheat sheet” for expert programmersì MIPS commands, registers, memory conventions, Computer Systems and NetworksSpring 2021

ìStarting on page 51 is an overview of the MIPS assembly commands! ìMIPS_Green_Sheet.pdf ì“Cheat sheet” for expert programmers ìMIPS commands, registers, memory conventions, Computer Systems and Networks Spring 2021 47