Transcription

Instruction Set ArchitectureEE33761–Adaptedfrom notes from BYU ECE124

Topics to Cover l l l l l l l l MSP430 ISAMSP430 Registers, ALU, MemoryInstruction FormatsAddressing ModesDouble Operand InstructionsSingle Operand InstructionsJump InstructionsEmulated Instructions–2http://en.wikipedia.org/wiki/TI MSP430–Adaptedfrom notes from BYU ECE124

Levels of Transformation–Problems–Algorithms–C Instructions–Assembly–LanguageMSP 430 ISA–Language–Machine(Program)(ISA) –Devices3–Adaptedfrom notes from BYU ECE124

Instruction Set Architecturel The computer ISA defines all of the programmer-visiblecomponents and operations of the computer–––l 4memory organizationl address space -- how may locations can be addressed?l addressibility -- how many bits per location?register set (a place to store a collection of bits)l how many? what size? how are they used?instruction setl Opcodes (operation selection codes)l data types (data types: byte or word)l addressing modes (coding schemes to access data)ISA provides all information needed for someone thatwants to write a program in machine language (or translatefrom a high-level language to machine language).–Adaptedfrom notes from BYU ECE124

MSP430 Instruction Set Architecturel MSP430 CPU specifically designed to allowthe use of modern programming techniques,such as:–––l l 5the computation of jump addressesdata processing in tablesuse of high-level languages such as C.64KB memory space with 16 16-bit registersthat reduce fetches to memory.Implements RISC architecture with 27instructions and 7 addressing modes.–Adaptedfrom notes from BYU ECE124

MSP430 16-bit RISCl l l l l l 6Orthogonal architecture with every instructionusable with every addressing mode.Full register access including program counter,status registers, and stack pointer.Single-cycle register operations.16-bit address bus allows direct access andbranching throughout entire memory range.16-bit data bus allows direct manipulation of wordwide arguments.Word and byte addressing and instruction formats.–Adaptedfrom notes from BYU ECE124

MSP430 Registersl The MSP430 CPU has 16 registers––l R0 (PC) – Program Counter–––7Large 16-bit register file eliminates single accumulatorbottleneckHigh-bandwidth 16-bit data and address busThis register always points to the next instruction to befetchedEach instruction occupies an even number of bytes.Therefore, the least significant bit (LSB) of the PCregister is always zero.After fetch of an instruction, the PC register isincremented by 2, 4, or 6 to point to the next instruction.–Adaptedfrom notes from BYU ECE124

MSP430 Registersl R1 (SP) – Stack Pointer–––––8The MSP430 CPU stores the return address of routinesor interrupts on the stackUser programs store local data on the stackThe SP can be incremented or decrementedautomatically with each stack accessThe stack “grows down” thru RAM and thus SP must beinitialized with a valid RAM addressSP always points to an even address, so its LSB isalways zero–Adaptedfrom notes from BYU ECE124

MSP430 Registersl R2 (SR/CG1) – Status Register–––9The status of the MSP430 CPU is defined by a set ofbits contained in register R2This register can only be accessed through registeraddressing mode - all other addressing modes arereserved to support the constants generatorThe status register is used for clock selection, interruptenable/disable, and instruction result status–Adaptedfrom notes from BYU ECE124

R2 (SR) – Status RegisterVOverflow bit – set when arithmetic operation overflows thesigned-variable range.SCG1System clock generator 1 – turns off the SMCLK.SCG0System clock generator 0 – turns off the DCO dc generator.OSCOFF Oscillator off – turns off the LFXT1 crystal oscillator.CPUOFF CPU off – turns off the CPU.10GIEGeneral interrupt enable – enables maskable interrupts.NNegative bit – set when the result of a byte or word operationis negative.ZZero bit – set when the result of a byte or word operation is 0.CCarry bit – set when the result of a byte or word operationproduces a carry.–Adaptedfrom notes from BYU ECE124

R2 (SR) – Status Registerl R2 (SR/CG1), R3 (CG2) – Constant Generators–11Six different constants commonly used in programmingcan be generated using the registers R2 and R3, withoutadding a 16-bit extension word of code to the instructionRegisterAsConstantRemarksR200-Register modeR2(0)R2011000004hAbsolute mode 4, bit processingR21100008h 8, bit processingR300000hR3000100001h0, word processing 1R31000002h 2, bit processingR3110FFFFh-1, word processing–Adaptedfrom notes from BYU ECE124

MSP430 Registersl R4-R15 – General Purpose registers––––12The general purpose registers R4 to R15 can be usedas data registers, data pointers and indices.They can be accessed either as a byte or as a wordInstruction formats support byte or word accessesThe status bits of the CPU in the SR are updatedafter the execution of a register instruction.–Adaptedfrom notes from BYU ECE124

MSP430 ALUl 16 bit Arithmetic Logic Unit (ALU).––Performs instruction arithmetic andlogical operationsInstruction execution affects the stateof the following flags:l l l l –13Zero (Z)Carry (C)Overflow (V)Negative (N)The MCLK (Master) clock signaldrives the CPU.–Adaptedfrom notes from BYU ECE124

MSP430 Memory––––14Unified 64KB continuous memory mapSame instructions for data andperipheralsProgram and data in Flash or RAMwith no restrictionsDesigned for modern programmingtechniques such as pointers and fastlook-up tables–Adaptedfrom notes from BYU ECE124

Anatomy of an Instructionl Opcode––l Source Operand–l –151st data object manipulated by the instructionDestination Operand–l What the instruction does – verbMay or may not require operands – objects2nd data object manipulated by the instructionAlso where results of operation are stored.Addressing Modes–Adaptedfrom notes from BYU ECE124

Instruction Formatl There are three formats used to encodeinstructions for processing by the CPU core–––l l l 16Double operandSingle operandJumpsThe instructions for double and single operands,depend on the suffix used, (.W) word or (.B)byteThese suffixes allow word or byte data accessIf the suffix is ignored, the instruction processesword data by default–Adaptedfrom notes from BYU ECE124

Instruction Formatl The source and destination of the data operatedby an instruction are defined by the followingfields:–––––––17src: source operand address, as defined in As and S-regdst: destination operand address, as defined in Ad and D-regAs: addressing bits used to define the addressing mode used bythe source operandS-reg: register used by the source operandAd: Addressing bits used to define the addressing mode usedby the destination operandD-reg: register used by the destination operandb/w: word or byte access definition bit.–Adaptedfrom notes from BYU ECE124

MPS430 Instruction Formatsl Format I: Instructions with two operands:151413121110Op-codel 432Ad10D/S-regFormat II: Jump instructions:1514Op-code184Format II: Instruction with one operand:15l 513121110Condition987654321010-bit, 2’s complement PC offset–Adaptedfrom notes from BYU ECE124

3 Instruction Formats19–Adaptedfrom notes from BYU ECE124

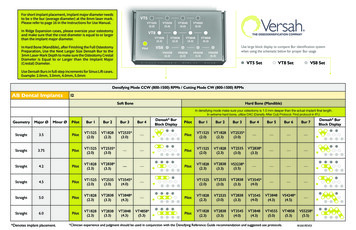

Double Operand Instructions20–Adaptedfrom notes from BYU ECE124

Single Operand Instruction21–Adaptedfrom notes from BYU ECE124

Jump Instructions22–Adaptedfrom notes from BYU ECE124

Source Addressing Modesl The MSP430 has four basic modes for thesource address:––––l In combination with registers R0-R3, threeadditional source addressing modes areavailable:––23Rs - Registerx(Rs) - Indexed Register@Rs - Register Indirect@Rs - Indirect Auto-increment–label - PC Relative, x(PC)&label – Absolute, x(SR)#n – Immediate, @PC –Adaptedfrom notes from BYU ECE124

Destination Addressing Modesl There are two basic modes for the destinationaddress:––l In combination with registers R0/R2, twoadditional destination addressing modes areavailable:––24Rd - Registerx(Rd) - Indexed Registerlabel - PC Relative, x(PC)&label – Absolute, x(SR)–Adaptedfrom notes from BYU ECE124

Register Mode (Rn)l The most straightforward addressing mode and isavailable for both source and destination– Example:mov.w r5,r6l l l 025; move word from r5 to r6The registers are specified in the instruction; no furtherdata is neededAlso the fastest mode and does not require an additioncycleByte instructions use only the lower byte, but clear theupper byte when daptedfrom notes from BYU ECE124

Indexed Mode x(Rn)The address is formed by adding a constant (index) to thecontents of a CPU register– Example:l mov.b 3(r5),r6Indexed addressing can be used for source and/ordestination, value in r5 is unchanged.The index is located in the memory word following theinstruction and requires an additional memory cycleThere is no restriction on the address for a byte, but wordsmust lie on even addressesl l l 026; move byte from; M(310 r5) to dfrom notes from BYU ECE124

Symbolic Mode (PC Relative)l The address if formed by adding a constant (index) to theprogram counter (PC)– Example: (mov.w x(PC), r6 where x Cnt-PC)mov.w Cnt,r6l l l 0The PC relative index is calculated by the assemblerProduces position-independent code, but rarely used in theMSP430 because absolute addressing can reach all memoryaddressesNote: this is NOT an appropriate mode of addressing whenreferencing fixed locations in memory such as the specialfunction registers (SFR’s)10Op-code27; move word; M(Cnt PC) to r60000S-reg000Adb/w01As0110D-reg–Adaptedfrom notes from BYU ECE124

Absolute Mode (&label)l The address is formed directly from a constant (index) andspecified by preceding a label with an ampersand (&)– Example: (mov.w x(SR), r6 where 0 is used for SR)mov.w &Cnt,r6l l l Same as indexed mode with the base register value of 0 (byusing the status register SR as the base register)The absolute address is stored in the memory word followingthe instruction and requires an additional cycleNote: this is the preferred mode of addressing when referencingfixed locations in memory such as the special function registers(SFR’s)028; move word; M(Cnt) to dfrom notes from BYU ECE124

Indirect Register Mode (@Rn)l The address of the operand is formed from the contents ofthe specified register– Example:mov.w @r5,r6l l l 029; move word; M(r5) to r6Only available for source operandsSame as indexed mode with index equal to 0, but does notrequire an additional instruction wordThe value of the indirect register is �Adaptedfrom notes from BYU ECE124

Indirect Autoincrement Mode (@Rn )l The address of the operand is formed from the contents of thespecified register and afterwards, the register is automaticallyincrement by 1 if a byte is fetched or by 2 if a word is fetched–Example:mov.w @r5 ,r6l l l Only available for source operands.Usually called post-increment addressing.Note: All operations on the first address are fully completedbefore the second address is evaluated030; move word; M(r5) to r6; increment r5 by from notes from BYU ECE124

Immediate Mode (#n)l The operand is an immediate value–Example (mov.w @PC , r6)mov.w #100,r6 ; 100 - r6l l l l The immediate value is located in the memory word followingthe instructionOnly available for source operandsThe immediate mode of addressing is a special case of autoincrement addressing that uses the program counter (PC) asthe source register.The PC is automatically incremented after the instruction isfetched; hence points to the following daptedfrom notes from BYU ECE124

Constant Generatorsl l 32The following source register/addressing modecombinations result in a commonly used constantoperand valueDo not require an additional instruction word–Adaptedfrom notes from BYU ECE124

Addressing Summary33–Adaptedfrom notes from BYU ECE124

Addressing Modes34–Adaptedfrom notes from BYU ECE124

Format I: Double Operandl Double operand instructions:MnemonicOperationDescriptionADD(.B or .W) src,dstsrc dst dstAdd source to destinationADDC(.B or .W) src,dstsrc dst C dstAdd source and carry to destinationDADD(.B or .W) src,dstsrc dst C dst (dec)Decimal add source and carry to destinationSUB(.B or .W) src,dstdst .not.src 1 dstSubtract source from destinationSUBC(.B or .W) src,dstdst .not.src C dstSubtract source and not carry from destinationArithmetic instructionsLogical and register control instructionsAND(.B or .W) src,dstsrc.and.dst dstAND source with destinationBIC(.B or .W) src,dst.not.src.and.dst dstClear bits in destinationBIS(.B or .W) src,dstsrc.or.dst dstSet bits in destinationBIT(.B or .W) src,dstsrc.and.dstTest bits in destinationXOR(.B or .W) src,dstsrc.xor.dst dstXOR source with destinationCMP(.B or .W) src,dstdst-srcCompare source to destinationMOV(.B or .W) src,dstsrc dstMove source to destinationData instructions35–Adaptedfrom notes from BYU ECE124

Example: Double Operandl Copy the contents of a register to another register––l l Assembly:mov.w r5,r4Instruction code: terD-regr40100010100000100One word instructionThe instruction instructs the CPU to copy the 16-bit 2’scomplement number in register r5 to register r436–Adaptedfrom notes from BYU ECE124

Example: Double Operandl Copy the contents of a register to a PC-relative memoryaddress location––Assembly:mov.w r5,TONIInstruction code: terD-regPC01000101100000002’s complement PC-relative destination indexl l 37Two word instructionThe instruction instructs the CPU to copy the

MSP430 Instruction Set Architecture ! MSP430 CPU specifically designed to allow the use of modern programming techniques, such as: – the computation of jump addresses – data processing in tables – use of high-level languages such as C. ! 64KB memory space with 16 16-bit registers that reduce fetches to File Size: 845KBPage Count: 60