Transcription

ESE 570: Digital Integrated Circuits andVLSI FundamentalsLec 1: September 2, 2020Introduction and OverviewPenn ESE 570 Fall 2020 - Khanna

Questions?!Use chat panel to type question"!Scroll to bottom of zoom window and click “chat”buttonOr just type “I have a question” and I will call onyou to unmute"Just like raising your hand in personPenn ESE 570 Fall 2020 - Khanna3

Your First Priority!Your first priority is your health"You should abide by all health guidelines""""""Part of your health is your mental and emotional health""Wear a maskWash your handsDon’t touch your faceMaintain social physical distancing" Virtual social interaction is encouraged!Stay home if you’re sickSee https://caps.wellness.upenn.edu/selfhelp/ for helpFor esPenn ESE 570 Fall 2020 - Khanna4

Advice for Remote Learning Success!Attend lecture in real time and stay on schedule""!Start homework early!""!Rewatch recorded lectures, attend virtual office hoursWe are here to help, but you need to let us know you need helpCadence is tricky, takes time to learn how to use it efficientlyWill give advice in lectures, but it won’t help if you haven’t startedUseful study habits ssets/rll-docs/Study%20Habits.pdfPenn ESE 570 Fall 2020 - Khanna5

I want to hear from you !Accessibility Survey in Canvas"!!!!Submit by Friday for full HW creditWill you be in a different time zone?Will you have trouble seeing or hearing videolectures?Are there any other accessibility issues I shouldknow about?Let me know any concerns -- I will do everything Ican to ensure you achieve the learning objectivesPenn ESE 570 Fall 2020 - Khanna6

Where I come from!!Analog VLSI Circuit Design (analog design)Convex Optimization (system design)"!!Biomedical ElectronicsBiometric Data Acquisition (signal processing)"!!System Hierarchical OptimizationCompressive SamplingADC Design (mixed signal)Low Energy Circuits (digital design)"Adiabatic ChargingPenn ESE 570 Fall 2020 – Khanna7

Where I come from!!Analog VLSI Circuit Design (analog design)Convex Optimization (system design)"!!Biomedical ElectronicsBiometric Data Acquisition (signal processing)"!!System Hierarchical OptimizationCompressive SamplingADC Design (mixed signal)Low Energy Circuits (digital design)"Adiabatic ChargingCIRCUITS, CIRCUITS, CIRCUITSPenn ESE 570 Fall 2020 – Khanna8

Lecture Outline!!!!!!!Course Topics OverviewLearning ObjectivesCourse StructureCourse PoliciesCourse ContentIndustry TrendsDesign ExamplePenn ESE 570 Fall 2020 - Khanna9

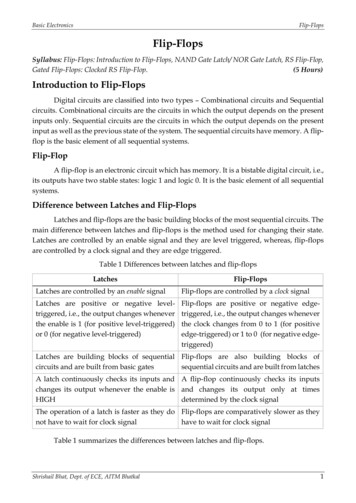

Course Topics OverviewCourse TopicsSystem-Related e ProgressionDesignμPs, Custom LogicVLSI Sub-systemsRegular StructuresROMs, RAMs, PLAsLogic Circuits, Gates, LatchesImplementation/FabricationTwo Transistor Logic Circuits (Inverters)StaticDynamicMOS Transistor, Capacitor and Interconnect ModelsCMOS FabricationPenn ESE 570 Fall 2020 - Khanna10

Learning Objectives!!!!!!Apply principles of hierarchical digital CMOS VLSI, from the transistor upto the system level, to the understanding of CMOS circuits and systems thatare suitable for CMOS fabrication.Apply the models for state-of-the-art(ish) VLSI components, fabricationsteps, hierarchical design flow and semiconductor business economics to judgethe manufacturability of a design and estimate its manufacturing costs.Design digital circuits that are manufacturable in CMOS.Design simulated experiments using Cadence to verify the integrity of aCMOS circuit and its layout.Apply the Cadence VLSI CAD tool suite layout digital circuits for CMOSfabrication and verify said circuits with layout parasitic elements.Apply course knowledge and the Cadence VLSI CAD tools in a team basedcapstone design project that involves much the same design flow they wouldencounter in a semiconductor design industrial setting. Capstone project ispresented in a formal report due at the end of the semester.Penn ESE 570 Fall 2020 - Khanna11

Learning Objectives!In other words !Design in CADENCE**All the way to layout/manufacturabilityPenn ESE 570 Fall 2020 - Khanna12

What is Cadence?!!Industry standard CAD software for IC designSchematic capture"!SPECTRE/SPICE simulator"!!Create netlist (software code describing schematic)Mathematical solver of differential equations describingfundamentals (Ex. KCL/KVL, Ohm’s law, etc.)Design physical mask layers used for fabricationExtract parasitics from physical layout forsimulationPenn ESE 570 Fall 2020 - Khanna13

Schematic CapturePenn ESE 570 Fall 2020 - Khanna14

Schematic CapturePenn ESE 570 Fall 2020 - Khanna15

Layout in CadencePenn ESE 570 Fall 2020 - Khanna16

Course Structure!MW Lecture, 4:30-6:00pm in Zoom""!Start 5 minutes after, end 5 minutes early ( 75-80min)Recordings posted in Canvas afterwardsWebsite (http://www.seas.upenn.edu/ ese570/)"""Course calendar is used for all handouts (lectures slides,assignments, and readings)Canvas used for assignment submission and gradesPiazza used for announcements and discussions"Use for Zoom links for lectures and OHsPenn ESE 570 Fall 2020 - Khanna17

Course Structure!!Course Staff (complete info on course website)Instructor: Tania Khanna"Office hours – WF 1-3 pm or by appointment""Email: taniak@seas.upenn.edu"!See Piazza for OH Zoom linkBest way to reach meTAs:"Yuanlong Xiao"Office hours: T 3-4:40pm, Th 9-10:30amPenn ESE 570 Fall 2020 - Khanna18

Additional TAsPenn ESE 570 Fall 2020 - Khanna19

Course Structure!Lectures""Statistically speaking, you will do better if you come tolectureBetter if interactive, everyone engaged""!Asking and answering questionsActively thinking about materialTextbook"CMOS Digital Integrated Circuits Analysis and Design,Kang, Leblebici, and Kim, 4th edition""Class will follow this text structureAdditional useful texts on course websitePenn ESE 570 Fall 2020 - Khanna20

Course Structure!Cadence""Technology: AMI .6u C5N (3M, 2P, high-res)Schematic simulation (SPECTRE simulator)""""Design, analysis and testLayout and verificationAnalog extracted simulationVerilog"HW 8 For Extra CreditPenn ESE 570 Fall 2020 - Khanna21

Course Structure - Assignments/Exams!Homework – 1 week long (8 total) [30%]""!Due Fridays at midnightHW 1 out nowProjects – 2 weeks long [50%]""Design orientedProjects""!Two projects combine to design and layout combinational logicblock used in FPGAsProj 1 – 20%, Proj 2 – 30%Midterm exam [20%]Penn ESE 570 Fall 2020 - Khanna22

Course PoliciesSee web page for full details! Turn homework in Canvas"""Anything handwritten/drawn must be clearly legibleSubmit CAD generated figures, graphs, results whenspecifiedLate Policy – allowed 4 late days for whole semester"!Can only use a max of one day on projectsIndividual work""CAD drawings, simulations, analysis, writeupsMay discuss strategies, but acknowledge helpPenn ESE 570 Fall 2020 - Khanna23

Course Content!!!!!!!IntroductionFabricationMOS Transistor Theory andModelsMOS Models and IVcharacteristicsInverters: Static Characteristicsand PerformanceInverters: DynamicCharacteristics and PerformanceCombinational Logic Types(CMOS, Ratioed, Pass) andPerformancePenn ESE 570 Fall 2020 - Khanna!!!!!!!Sequential LogicDynamic LogicVLSI design and ScalingMemory DesignI/O Circuits and InductiveNoiseCLK GenerationTransmission Lines24

Course Contenthttps://www.seas.upenn.edu/ ese570/fall2020/syllabus.htmlPenn ESE 570 Fall 2020 - Khanna25

Industry TrendsPenn ESE 570 Fall 2020 - Khanna26

Microprocessor Trans Count 1971-2015Curve showstransistor countdoubling everytwo yearsPentium16-Core SPARC T310-Core Xenon6-Core6-Corei7i7IBM 4-Core z1962-Core Itanium 2IBM 8-Core POWER74-Core Itanium TukwillaAMD K10AMD 6-Core Opteron4-Core i7 2400AMD K8Pentium 4AMD K7Pentium IIIPentium IIAMD K5804868038680286Mot 68000801868086Mot 68008080Zilog Z808006MOS 650240042015: Oracle SPARC M7, 20 nm CMOS,32-Core, 10B 3-D FinFET transistors.Kenneth R. Laker, University of Pennsylvania, updated20Jan15PennESE 570 Fall 2020 - Khanna201527

Intel Cost 4nm-technologyin-detailPenn ESE 570 Fall 2020 - Khanna28

Trend – “Minimum” Feature Size vs. YearProcess Node/”Minimum” Feature100 µmIntegrated CircuitHistory10 µm1 µmITRS Roadmap0.18 µm in 19990.1 µm10 nm“Distant” Future?Transition Region1 nmQuantum DevicesAtomic Dimensions0.1 nm19601980200020202040Year“Minimum” Feature Measure line/gate conductor width or half-pitch (adjacent1st metal layer lines or adjacent transistor gates)Penn ESE 570 Fall 2020 - Khanna29

More Moore # Scaling!Geometrical Scaling"!Equivalent Scaling"!continued shrinking of horizontal and vertical physicalfeature sizes3-dimensional device structure improvements and newmaterials that affect the electrical performance of the chipeven if no geometrical scalingDesign Equivalent Scaling"design technologies that enable high performance, lowpower, high reliability, low cost, and high designproductivity even if neither geometrical nor equivalentscaling can be usedPenn ESE 570 Fall 2020 - Khanna30

22nm 3D FinFET TransistorHigh-kTri-Gate transistors with multiplegatefins connected togetherdielectric increases total drive strength forhigher /22nm/pdfs/22nmDetails Presentation.pdfPenn ESE 570 Fall 2020 - Khanna31

ITRS 2.0 Report 2015!“After 2021, the report forecasts, it will no longer be economicallydesirable for companies to continue traditional transistor miniaturizationin microprocessors.”Penn ESE 570 Fall 2020 - Khanna32

BUT ng-moores-law.pdfPenn ESE 570 Fall 2020 - Khanna33

BUT ng-moores-law.pdfPenn ESE 570 Fall 2020 - Khanna34

More than Moore # Functional Diversification!Interacting with the outside world"Electromagnetic/Optical""""Mechanical parameters (sensors/actuators)"""!Radio-frequency domain up to the THz rangeOptical domain from the infrared to the near ultravioletHard radiation (EUV, X-ray, γ-ray)MEMS/NEMS position, speed, acceleration, rotation,pressure, stress, etc.Chemical composition (sensors/actuators)Biological parameters (sensors/actuators)Power/Energy"Integration of renewable sources, Energy storage, Smartmetering, Efficient consumptionPenn ESE 570 Fall 2020 - Khanna35

ScalingMore-than-Moore“More-than-Moore”, International Road Map(IRC) White Paper, 2011.International Technology Roadmap for SemiconductorsPenn ESE 570 Fall 2020 - Khanna36

“More-than-Moore”!Components Complement Digital Processing/Storage Elements in an Integrated SystemPenn ESE 570 Fall 2020 - Khanna37

MicroImplant: An Electronic Platform forMinimally Invasive Sensory MonitorsPenn ESE 570 Fall 2020 - Khanna38

Semiconductor System Integration – MoreThan Moore's 2Transistors/cm2108SOP law for system integration.As components shrink and boards all butdisappear, component density will doubleevery year or so.2020R. Tummala, “Moore's Law Meets Its Match”, IEEE Spectrum, June, 2006Penn ESE 570 Fall 2020 - Khanna39

Societal NeedsPenn ESE 570 Fall 2020 - Khanna40

Improvement Trends for VLSI SoCs Enabledby Geometrical and Equivalent Scaling!!TRENDS:Higher Integration level"!!combination of Geometrical(shrinking of dimensions)and Equivalent (innovation)Scaling.!!SoC increased use of SiP SOPDecreasing energyrequirement per function.Lower Cost"Penn ESE 570 Fall 2020 - Khannaincreasingsystem integration.Lower Power"!CPU clock rate at multipleGHz parallel processing.Increased Compactness &less weight"System implementation"CONSEQUENCES:Higher Speed"Performance Scaling"!exponentially increasednumber of components/transistors per chip/package.!Decreasing cost perfunction.41

Trends in Practice at ISSCC (HW 1)Penn ESE 570 Fall 2020 - Khanna42

Design ExamplePenn ESE 570 Fall 2020 - Khanna

VLSI Design Cycle or FlowVerilog/SPICEPenn ESE 570 Fall 2020 - Khanna44

VLSI Design Cycle or FlowFunctional Specification:Verilog/SPICEPenn ESE 570 Fall 2020 - Khanna45

Illustrative Circuit Design Example: VLSI Design!8-bit Ripple AdderPenn ESE 570 Fall 2020 - Khanna46

Illustrative Circuit Design Example: System RequirementsFunctional Specification:Penn ESE 570 Fall 2020 - Khanna47

Illustrative Circuit Design Example: Architecture DefinitionPenn ESE 570 Fall 2020 - Khanna48

Illustrative Circuit Design Example: Logic Design!Gate Level Schematic of One-Bit Full Adder CircuitPenn ESE 570 Fall 2020 - Khanna49

VLSI Design Cycle or FlowDesign Specifications:Penn ESE 570 Fall 2020 - KhannaVerilog/SPICE50

Illustrative Circuit Design Example: System RequirementsFunctional Specification:Design Specifications (in 0.8 twin-well CMOS):1. Propagation Delay Times of SUM and CARRY Out signals: 1.2 ns2. Rise and Fall Times of SUM and CARRY Out signals: 1.2 ns3. Circuit Die Area: 1500 um24. Dynamic Power Dissipation (@ VDD 5 V and f max 20 MHz): 1 mWPenn ESE 570 Fall 2020 - Khanna51

Illustrative Circuit Design Example: VLSI Design!Transistor Level Schematic of One-Bit Full Adder CircuitPenn ESE 570 Fall 2020 - Khanna52

Illustrative Circuit Design Example: VLSI Design and LayoutCOUTSUMOUTN1N2COUTN1Penn ESE 570 Fall 2020 - KhannaN253

Illustrative Circuit Design Example: VLSI Design and Layout!Initial Layout of One-Bit Full Adder CircuitCOUT 1500 um2Dynamic Power Dissipation (@ VDD 5V, f max 20 MHz): 0.7 mW 1 mWPenn ESE 570 Fall 2020 - Khanna54

Post Layout Simulation (Analog extracted)Schematicto layoutPenn ESE 570 Fall 2020 - Khanna55

Post Layout Simulation (Analog extracted)Layout toschematicPenn ESE 570 Fall 2020 - Khanna56

Illustrative Circuit Design Example: Design VerificationSpec NOTmetPenn ESE 570 Fall 2020 - Khanna57

Admin!Find web, get text, assigned reading """!!Submit Accessibility SurveyHW 1 posted now"!!http://www.seas.upenn.edu/ ps://canvas.upenn.edu/Due next week Sept 11If you’re outside the US email me ASAP to testaccess to CadenceRemaining Questions?Penn ESE 570 Fall 2020 - Khanna58

Study%20Habits.pdf Penn ESE 570 Fall 2020 - Khanna 5 . . " CMOS Digital Integrated Circuits Analysis and Design, Kang, Leblebici, and Kim, 4th edition " Class will follow this text structure " Additional useful tex