Transcription

TMS320x281x Serial Peripheral InterfaceReference GuideLiterature Number: SPRU059EJune 2002 – Revised February 2009

2SPRU059E – June 2002 – Revised February 2009Submit Documentation Feedback

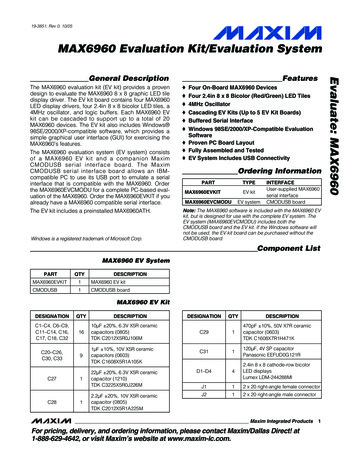

ContentsPreface . 711.11.21.31.41.5. 9Enhanced SPI Module Overview . 101.1.1 SPI Block Diagram . 121.1.2 SPI Module Signal Summary . 13Overview of SPI Module Registers . 13SPI Operation . 141.3.1 Introduction to Operation . 141.3.2 SPI Module Slave and Master Operation Modes . 15SPI Interrupts . 161.4.1 SPI Interrupt Control Bits . 161.4.2 Data Format . 171.4.3 Baud Rate and Clocking Schemes . 181.4.4 Initialization Upon Reset. 201.4.5 Data Transfer Example . 20SPI FIFO Description . 211.5.1 SPI Interrupts . 22Serial Peripheral Interface (SPI). 252SPI Registers and Waveforms2.1SPI Control Registers . 262.2.2.1.3 SPI Status Register (SPIST) .2.1.4 SPI Baud Rate Register (SPIBRR) .2.1.5 SPI Emulation Buffer Register (SPIRXEMU) .2.1.6 SPI Serial Receive Buffer Register (SPIRXBUF) .2.1.7 SPI Serial Transmit Buffer Register (SPITXBUF) .2.1.8 SPI Serial Data Register (SPIDAT) .2.1.9 SPI FIFO Transmit, Receive, and Control Registers .2.1.10 SPI Priority Control Register (SPIPRI) .SPI Example Waveforms .ARevision History2.1.1SPI Configuration Control Register (SPICCR)262.1.2SPI Operation Control Register (SPICTL)27282929303031323536. 39SPRU059E – June 2002 – Revised February 2009Submit Documentation FeedbackContents3

www.ti.comList of -82-92-102-112-122-132-142-152-162-172-184SPI CPU Interface .Serial Peripheral Interface Module Block Diagram .SPI Master/Slave Connection .SPICLK Signal Options .SPI: SPICLK-CLKOUT Characteristic When (BRR 1) is Odd, BRR 3, and CLOCK POLARITY 1 .Five Bits per Character .SPI FIFO Interrupt Flags and Enable Logic Generation .SPI Configuration Control Register (SPICCR) — Address 7040h .SPI Operation Control Register (SPICTL) — Address 7041h .SPI Status Register (SPIST) — Address 7042h .SPI Baud Rate Register (SPIBRR) — Address 7044h .SPI Emulation Buffer Register (SPIRXEMU) — Address 7046h.SPI Serial Receive Buffer Register (SPIRXBUF) — Address 7047h .SPI Serial Transmit Buffer Register (SPITXBUF) — Address 7048h .SPI Serial Data Register (SPIDAT) — Address 7049h .SPI FIFO Transmit (SPIFFTX) Register – Address 704Ah .SPI FIFO Receive (SPIFFRX) Register – Address 704Bh .SPI FIFO Control (SPIFFCT) Register – Address 704Ch .SPI Priority Control Register (SPIPRI) — Address 704Fh .CLOCK POLARITY 0, CLOCK PHASE 0 (All data transitions are during the rising edge, non-delayedclock. Inactive level is low.) .CLOCK POLARITY 0, CLOCK PHASE 1 (All data transitions are during the rising edge, but delayedby half clock cycle. Inactive level is low.) .CLOCK POLARITY 1, CLOCK PHASE 0 (All data transitions are during the falling edge. Inactivelevel is high.) .CLOCK POLARITY 1, CLOCK PHASE 1 (All data transitions are during the falling edge, but delayedby half clock cycle. Inactive level is high.) .SPISTE Behavior in Master Mode (Master lowers SPISTE during the entire 16 bits of transmission.) .SPISTE Behavior in Slave Mode (Slave’s SPISTE is lowered during the entire 16 bits of transmission.) .List of 7373838SPRU059E – June 2002 – Revised February 2009Submit Documentation Feedback

www.ti.comList of -112-122-13A-1SPI Module Signal Summary .SPI Registers .SPI Clocking Scheme Selection Guide .SPI Interrupt Flag Modes .SPI Configuration Control Register (SPICCR) Field Descriptions .Character Length Control Bit Values .SPI Operation Control Register (SPICTL) Field Descriptions .SPI Status Register (SPIST) Field Descriptions .Field Descriptions .SPI Emulation Buffer Register (SPIRXEMU) Field Descriptions .SPI Serial Receive Buffer Register (SPIRXBUF) Field Descriptions .SPI Serial Transmit Buffer Register (SPITXBUF) Field Descriptions .SPI Serial Data Register (SPIDAT) Field Descriptions .SPI FIFO Transmit (SPIFFTX) Register Field Descriptions .SPI FIFO Receive (SPIFFRX) Register Field Descriptions .SPI FIFO Control (SPIFFCT) Register Field Descriptions .SPI Priority Control Register (SPIPRI) Field Descriptions .Changes in Revision E .SPRU059E – June 2002 – Revised February 2009Submit Documentation FeedbackList of Tables1313192226272728293030313132333435395

6List of TablesSPRU059E – June 2002 – Revised February 2009Submit Documentation Feedback

PrefaceSPRU059E – June 2002 – Revised February 2009This guide describes how the serial peripheral interface works.About This ManualThe SPI module described in this reference guide is a Type 0 SPI. See the TMS320x28xx, 28xxx DSPPeripheral Reference Guide (SPRU566) for a list of all devices with an SPI module of the same type, todetermine the differences between types, and for a list of device-specific differences within a type.Related Documentation From Texas InstrumentsThe following books describe the TMS320x281x and related support tools that are available on the TIwebsite.CPU User's Guides—SPRU430— TMS320C28x DSP CPU and Instruction Set Reference Guide describes the centralprocessing unit (CPU) and the assembly language instructions of the TMS320C28x fixed-pointdigital signal processors (DSPs). It also describes emulation features available on these DSPs.SPRU078— TMS320x281x System Control and Interrupts Reference Guide describes the variousinterrupts and system control features of the 281x digital signal processors (DSPs).Peripheral Guides—SPRU566— TMS320x28xx, 28xxx DSP Peripheral Reference Guide describes the peripheral referenceguides of the 28x digital signal processors (DSPs).SPRU060— TMS320x281x Analog-to-Digital Converter (ADC) Reference Guide describes the ADCmodule, which is a 12-bit pipelined ADC. The analog circuits of this converter, referred to as thecore in this document, include the front-end analog multiplexers (MUXs), sample-and-hold (S/H)circuits, the conversion core, voltage regulators, and other analog supporting circuits. Digitalcircuits, referred to as the wrapper in this document, include programmable conversion sequencer,result registers, interface to analog circuits, interface to device peripheral bus, and interface to otheron-chip modules.SPRU065— TMS320x281x Event Manager (EV) Reference Guide describes the EV modules that providea broad range of functions and features that are particul

SPRU059— TMS320x28xx, 28xxx Serial Peripheral Interface (SPI) Reference Guide describes the SPI - a high-speed synchronous serial input/output (I/O) port - that allows a serial bit stream of programmed length (one to sixteen bits) to be shifted into and out of the device at a programmed