Transcription

JULY 2021 VOL. 28, NO. 3 ISSN: 1074 1879TableofContentsEDITOR-IN-CHIEF: DANIEL TOMASZEWSKITechnical BriefsTECHNICAL BRIEFS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Beyond CMOS (BC) An Introduction to SiC Power Devices: Status,Challenges, and Outlook A Review of the 22nd International VacuumElectronics Conference (IVEC)UPCOMING TECHNICAL MEETINGS. . . . . . . . . . . . . . . . . . . . 20 2021 IEEE International Electron DevicesMeeting (IEDM) 2021 IEEE BiCMOS and CompoundSemiconductor Integrated Circuits andTechnology Symposium (BCICTS)SOCIETY NEWS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 EDS Board of Governors Meeting Summary Message from EDS Newsletter Editor-in-Chief EDS Board of Governors Call for Nominations EDS Board of Governors Election ProcessEDS AWARDS AND CALLS FOR NOMINATIONS. . . . . . . . . 26 2021 IEEE William R. Cherry Award Winner EDS Chapter of the Year Award Call for Nominations Region 9 Outstanding Student Paper Award Solicitationfor NominationsEDS WOMEN IN ENGINEERING. . . . . . . . . . . . . . . . . . . . . . . 29 Susan Lord—Cutting Ties, Forging Paths,and Speaking Up Nadine Collaert—My Wonderful Journey in Scienceand Engineering IEEE Electron Devices Society’s InternationalWomen’s Day (IWD) EventEDS YOUNG PROFESSIONALS. . . . . . . . . . . . . . . . . . . . . . . . 33 Luisa Petti: Reflections from an EDS YoungProfessional Manan Suri: Reflections from an EDS YoungProfessional Updates from the 2020 EDS PhD StudentFellowship Winners Updates from the 2020 EDS Masters StudentFellowship Winners Updates from the 2020 EDS UndergraduateFellowship WinnersEDS HUMANITARIAN PROJECTS . . . . . . . . . . . . . . . . . . . . . 39 2020 IEEE Industry Placement Scheme Sponsorships Towards Industrial Placementby the IEEE EDS Society IEEE TryEngineering PortalCHAPTER NEWS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 Spotlight on ED Delhi Chapter IEEE EDS Center of Excellence at HeritageInstitute of TechnologyREGIONAL NEWS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44Beyond CMOS (BC)Matthew Marinella1, Shamik Das2, Sapan Agarwal1,Michael P. Frank1, Hiro Akinaga3, An Chen4Sandia National Laboratories*, 2MITRE**, 3National Institute ofAdvanced Industrial Science and Technology (AIST), 4IBM Research*Sandia National Laboratories is a multi-mission laboratory managed andoperated by National Technology & Engineering Solutions of Sandia, LLC,a wholly owned subsidiary of Honeywell International Inc., for the U.S.Department of Energy’s National Nuclear Security Administration under contract DE-NA0003525. Approved for public release SAND2021-6396 O.**Approved by The MITRE Corporation for Public Release; DistributionUnlimited. Public Release Case Number 20-02213-5.1I. IntroductionCMOS scaling has driven a broad spectrum of applications throughincreased performance and complexity. As dimensional scaling ofCMOS eventually approaches fundamental limits, new informationprocessing devices and architectures have been explored extensively in both academia and industry. The Beyond CMOS (BC) chapter in the International Roadmap for Devices and Systems (IRDS)surveys, catalogs, and assesses viable emerging devices and novelarchitectures for their long-range potential, and identifies the scientific and technological challenges gating their acceptance by thesemiconductor industry. In the previous International TechnologyRoadmap for Semiconductors (ITRS), the Emerging Research Devices (ERD) chapter covered a similar scope. The BC chapter in IRDShas inherited certain content, structure, and methodology fromthe ERD chapter in ITRS. During the transition from ITRS to IRDS,the importance of co-optimization of emerging devices and architectures has been increasingly recognized in the broad researchcommunity. Therefore, beyond the traditional focus on emergingmemory and logic devices, the BC chapter has placed significantemphasis on emerging device-architecture interactions.(continued on page 3)EDS MEETING CALENDAR. . . . . . . . . . . . . . . . . . . . . . . . . . . 53EDS MISSION, VISION AND FIELD OF INTERESTSTATEMENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56Your Comments SolicitedYour comments are most welcome. Please write directly to theEditor-in-Chief of the Newsletter atdaniel.tomaszewski@imif.lukasiewicz.gov.pl

ELECTRON DEVICESNEWSLETTERSOCIETYEDITORIAL STAFFPresidentRavi TodiWestern Digital TechnologiesEmail: rtodi@ieee.orgTreasurerBin ZhaoFreescale SemiconductorEmail: bin.zhao@ieee.orgSecretaryM.K. RadhakrishnanNanoRelEmail: radhakrishnan@ieee.orgJr. Past PresidentFernando GuarinGlobalFoundriesEmail: fernando.guarin@ieee.orgSr. Past PresidentSamar SahaProspicient DevicesEmail: samar@ieee.orgVice President of EducationNavakanta BhatIndian Institute of ScienceEmail: navakant@gmail.comVice President of MeetingsKazunari IshimaruKioxia CorporationEmail: kazu.ishimaru@kioxia.comEditor-In-ChiefDaniel TomaszewskiInstitute of Microelectronics and PhotonicsEmail: daniel.tomaszewski@imif.lukasiewicz.gov.plVice President of Membershipand ServicesPatrick FayUniversity of Notre DameEmail: pfay@nd.eduAssociate Editor-in-ChiefManoj SaxenaDeen Dayal Upadhyaya CollegeUniversity of DelhiEmail: msaxena@ieee.orgScandinavia & Central EuropeREGIONS 1–6, 7 & 9Marcin JanickiEastern, Northeastern &Lodz University of TechnologySoutheastern USAEmail: janicki@dmcs.pl(Regions 1, 2 & 3)Rinus LeeUnited Kingdom, MiddleTEL Technology Center, AmericaEast & AfricaEmail: rinuslee@ieee.orgStewart SmithCentral USA & CanadaScottish Microelectronics Centre(Regions 4 & 7)Email: stewart.smith@ed.ac.ukMichael AdachiWestern EuropeSimon Fraser UniversityMike SchwarzEmail: mmadachi@sfu.caMittelhessen University ofSouthwestern & Western USAApplied Sciences(Regions 5 & 6)Email: mike.schwarz1980@Muhammad Mustafa Hussaingooglemail.comUniversity of California—BerkeleyEmail: MuhammadMustafa.REGION 10Hussain@kaust.edu.saAustralia, New Zealand &South East AsiaLatin America North (Region 9)Sharma Rao BalakrishnanJoel Molina ReyesUniversiti Sains Islam MalaysiaINAOEEmail: sharma@usim.edu.myEmail: jmolina@inaoep.mxNorth East and East AsiaTuo-Hung HouLatin America South (Region 9)National Yang Ming Chiao TungPaula Ghedini Der AgopianUniversityUNESP, Sao Paulo State UniversityEmail: thhou@mail.nctu.edu.twEmail: paula.agopian@unesp.brVice President of Publicationsand ProductsJoachim BurghartzInstitute for MicroelectronicsStuttgartEmail: burghartz@ims-chips.deVice President of Regions/ChaptersMurty PolavarapuSpace Electronics SolutionsEmail: murtyp@ieee.orgVice President of StrategicDirectionsPaul BergerThe Ohio State UniversityEmail: pberger@ieee.orgVice President of TechnicalCommitteesJohn DallessaseUniversity of Illinois at UrbanaChampaignEmail: jdallesa@illinois.eduIEEE prohibits discrimination, harassment, and bullying. For more information,visit -26.html.REGION 8Eastern EuropeKateryna ArkhypovaIRE NASUEmail: arkhykate@ieee.orgEDS Board of Governors (BoG)Elected Members-at-LargeElected for a three-year term (maximum two terms) with ‘full’ voting privileges2021 Term 2022 Term 2023 TermPaul Berger(1) Constantin Bulucea (1) Roger BoothNavakanta Bhat(2) Daniel Camacho(1) Xiojun GuoMerlyne De Souza (1) John Dallesasse(1) Edmundo A. Gutierrez-D.Kazumari Ishimaru (1) Mario Lanza(1) Francesca IacopiWilliam (Bill) Nehrer (1) Geok Ing Ng(1) Benjamin IniguezMurty Polavarapu (2) Claudio Paoloni(1) P. Susthitha MenonCamilo Velez Cuervo (1) Hitoshi Wakabayashi (1) Manoj SaxenaSumant Sood(2)(1)(2)(1)(2)(1)(2)(2)South AsiaSoumya PanditUniversity of CalcuttaEmail: soumya pandit@ieee.orgContributions WelcomeReaders are encouraged to submit news items concerning the Society andits members. Please send your ideas/articles directly to either Editor-inChief or the Regional Editor for your region. The email addresses of allRegional Editors are listed on this page. Email is the preferred form ofsubmission.Newsletter DeadlinesIssueDue DateOctoberJanuaryAprilJulyJuly 1stOctober 1stJanuary 1stApril 1stThe EDS Newsletter archive can be found on the Society web site athttp://eds.ieee.org/eds-newsletters.html. The archive contains issues fromJuly 1994 to the present.IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and ElectronicsEngineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar ( 1.00) per member per year is included inthe Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Sendaddress changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.Copyright 2021 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies arenot used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.2IEEE Electron Devices Society Newsletter July 2021Promoting Sustainable ForestrySFI-01681

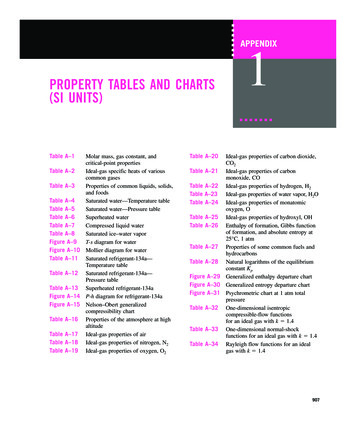

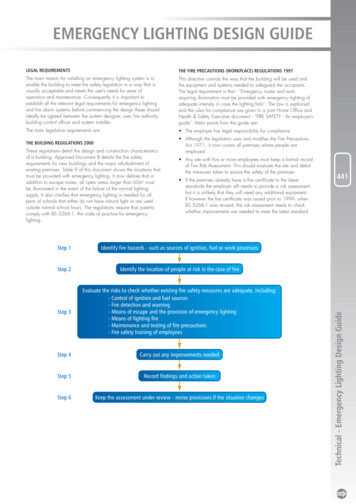

Beyond CMOS (BC)(continued from page 1)Although the semiconductor industry faces difficult challenges inCMOS dimensional scaling, there arepromising alternative directions forsustained improvement in chip performance and functionality. Integrating new high-speed, high-density,and low-power memory technologiesonto the CMOS platform may breakthe “ memory wall”, improve systemperformance, and enable new computing paradigms (e.g., in-memorycompute). Novel switches based onnew materials, alternative mechanisms, and non-charge state variables (e.g., steep-slope transistors,phase-transition devices, nonvolatileswitches) may achieve significantlybetter energy efficiency than CMOStransistors based on thermionicemission over the channel energybarrier. New information processingtechnologies substantially beyondthe capabilities of CMOS may originate from an innovative combinationof new devices, interconnect, andarchitecture for extending CMOS,which may eventually lead to newplatform technologies. Ultimatelyscaled CMOS as a platform technology may also extend into new domainof functionalities and applications(e.g., security, sensing, communication), a general direction knownas “more than Moore”. For all thesepromising directions beyond CMOSand dimensional scaling, new materials and integration techniques playessential roles to enable their implementations.The BC chapter covers the following major areas: 1) emerging memoryand storage devices, 2) emerging logicand alternative information processing devices, 3) emerging device-architecture interactions (includingnew computing paradigms), and 4)emerging materials integration. Thisarticle will briefly review these areasof research and present key observations and recommendations.II. Emerging Memoryand Storage DevicesMemory is an essential element ofcomputing, and the characteristicsof the memory device technologiesplay a significant role in the architecture of an information processing system. A taxonomy of currentmemory devices is given in Fig. 1.Static and dynamic random accessmemory (SRAM and DRAM) remainthe workhorse computing memorytechnologies, due to their high speedand endurance. Both are volatile andrequire backup storage when powered down. Nonvolatile memoryincludes flash, the most prominentand technologically mature baselinetechnology. The term “flash” refersto an array architecture for chargebased memory cells such as floatinggate and charge trapping memory,both of which serve as the main datastorage mechanism for most modern information processing systems.SRAM, DRAM, and Flash memoryhave followed Moore’s Law scaling for several decades, which wastracked by the ITRS until 2015 andis currently tracked by IRDS. Prototypical devices have matured tothe point where the technology is insmall-scale commercial production,and often the technology is makingprogress on factors such as scalingand density. In this case, prototypical devices that are making progresshave historically been tracked byITRS and expected future progressis predicted. These technologiesinclude ferroelectric memory (FeRAM), phase change memory (PCM),field-switched magnetic memory(MRAM), and spin transfer torquemagnetic memory (STT-MRAM).Several of these technologies, suchas STT-MRAM started in the emerging category and have progressed tothe prototypical phase and are continuing to progress commercially.The primary purpose of the Emerging Memory Devices section is to tracktechnical progress for those devices inthe rightmost “emerging” column. Thissection provides a technical overviewof each device, and is accompanied bytables that track key properties of thesedevices as reported in the literature,such as endurance, retention, switchingcharacteristics, and minimum dimensions.These emerging memory devicesare the subject of significant research,with potential to continue storage density scaling beyond physical limits offlash, improve computing efficiencyby enabling storage class memory,Figure 1. Emerging memory devices taxonomy.July 2021 IEEE Electron Devices Society Newsletter3

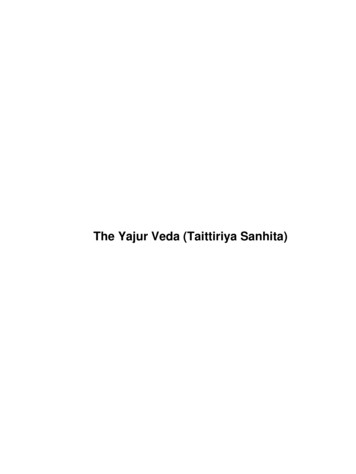

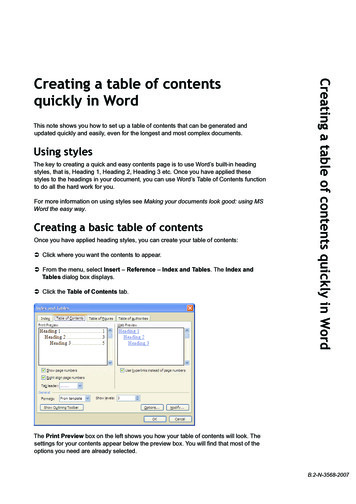

and enable new computing paradigmssuch as in-memory compute.One of the most active emergingmemory research topics is magneticmemories. STT-MRAM has made significant progress in the past decade,and recently we have seen the emergence of several commercial productsand integration in commercial foundries. This is due to excellent scalability, CMOS-compatible voltages, highendurance, and compatibility withback end of line CMOS processes. STTMRAM has the potential for future useas a cache replacement, [1] although itwill be important to reduce switchingcurrent, increase speed, and increaseenergy efficiency. This need for improved magnetic memory propertieshas prompted research in emergingmagnetic devices. One example is thethree terminal memory structure whichharnesses spin orbit torque (SOT) effect,reducing the current density required toswitch the magnetization of a magnetictunnel junction (MTJ). Another activearea of research is in voltage controlledmagnetic anisotropy (VCMA), whichharnesses magnetoelectric effects toreduce the energy and improve thespeed of MTJ switching [2].Resistive and conductive-bridgerandom access memory (ReRAM andCBRAM), have seen also significantcommercial interest and researchactivity in the literature, due to potential for applications such as storage class memory, edge computing,and efficient processing of neuralnetworks. These are two terminal resistive switching device structures,with a memory state defined by theresistance. This resistance is controlled by the connecting and breaking of metallic conductive filaments(CBRAM) or modulation of oxygenvacancy concentrations in a metaloxide (ReRAM). Resistive memoriesare highly scalable and CMOS-compatible, and hence are being integrated into foundry processes. Researchchallenges for these devices continueto be improving the understanding,parametric control, and reliability.Emerging polymer memories, whichincorporation organic materials, often rely on similar physical mechanisms to ReRAM and CBRAM [3].Ferroelectric memories, includingthe ferroelectric field effect transistor (FeFET) have seen a resurgenceof interest recently due to the discovery of ferroelectricity in HfO [4]which has provided a path for FeFETscalability and CMOS compatibility.Other new technologies that are fur-Figure 2. Taxonomy of logic devices beyond CMOS. Reproduced from Figure BC3.1 of the 2021IRDS Beyond CMOS chapter.4IEEE Electron Devices Society Newsletter July 2021ther from commercialization (and lackconcrete benchmarks) have becomethe subject of significant research. Forexample, DNA storage (covered under massive storage devices) has thehighest volumetric information storage capacity of any known medium,which has motivated research to tacklethe practical challenges of using thesecomplex organic molecules for information storage. It is hoped that theIRDS coverage of emerging memoriescan serve as a reference for the electron device community and engineersin understanding new memory devices and their impact on future computing systems, for funding agencies inunderstanding the memory researchchallenges, as well as for studentsand others in academia who need abetter understanding of the memoryresearch landscape.III. Emerging Logic andInformation Processing DevicesFor nearly twenty years, the industry’s semiconductor roadmap hasfeatured device options that mightsurpass silicon CMOS as the driverfor logic, computation, and information processing applications. Originally captured as Emerging ResearchDevices, recent editions of the IRDSpresent these as Logic Devices Beyond CMOS. Though silicon CMOShas proved exceptionally hardyand productive over the last twentyyears, the roadmap continues totrack Beyond-CMOS devices for bothnear-term successors and more disruptive, longer-term candidates.Figure 2 depicts the taxonomy ofemerging logic devices as conveyedin the IRDS. Such devices departfrom the present state-of-the-art intwo primary ways. First, the structureand materials constituting the devicewill be different to some degree fromsilicon planar FETs or FinFETs. Thisdeparture is shown on the horizontalaxis. Second, the physical manifestation of digital information, also knownas the state variable, may differ fromthe electric charge that is used inFETs. This is shown on the vertical

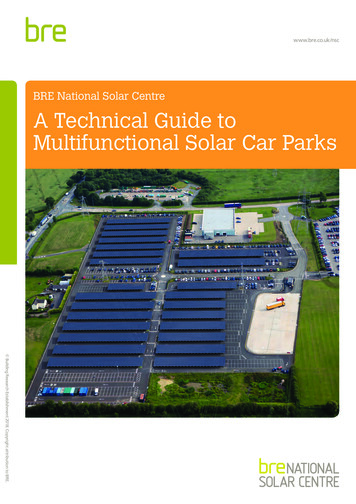

axis. Considering these elements together, a natural three-part groupingemerges that is used to characterizenear-term vs. far-term candidates forthe evolution of semiconductors.The nearest of these candidates arethe conventionally structured, chargebased devices listed in the lower leftof the figure. Such devices includenanowire transistors and carbonnanotube transistors, for example. Theintent with these devices is to obtaincharge transport characteristics exceeding the semiconductor channelsof conventional devices. Thus, a fewof these candidates could be considered as potential channel-replacementtechnologies for near-future state-ofthe-art devices and are also trackedwithin the “More Moore” componentof the IRDS. This includes “stackednanosheet” devices as well as verticalgate-all-around (VGAA) transistors.Further evolutions of charge-baseddevices are considered in the lowerright of the figure. Here, one beginsto see mechanisms for modulatingcharge transport that differ from theelectrostatic field effect. Some examples include using a type of metal-insulator phase transition (Motttransition) as a switch or using electromechanical potential to store adigital state. Because of the greaterdeparture in materials systems fromCMOS as compared with the first category of candidates, it is expected thatintegration with CMOS will be morecomplicated and take longer to manifest commercially. Also, it is less clearfor any of these devices that there isa route to the kind of universal performance applicability and scalabilitythat has made silicon CMOS economically viable for so long.A recent addition to the BeyondCMOS roadmap in this second groupof the figure is the topological insulator transistor. Research into topological insulators as materials hasincreased substantially in recentyears, primarily for applications inquantum information science. Someof these research results suggestroutes to using topological propertiesto increase the speed and power efficiency of field-effect devices. It is anongoing line of inquiry to determineif such advantages can be materialized robustly at room temperaturewith commercially relevant yields.Finally, the Beyond CMOS roadmap has always monitored the progress in devices shown at upper rightin the figure, which represent a substantial departure both in form andfunction from conventional semiconductor field-effect transistors.Principally, these devices use a noncharge-based state variable, such asa remnant magnetization, exciton, oroptical/photonic state. In some cases,state information can be transportedvia charges, such as with a spin-filtered electronic current. In others, thechange in state variable also requiresa novel form or material structure forthe interconnect. Thus, developmentand commercial maturation for thesecandidates is expected to take significant time, or else such devices mightonly be used within heterogeneousintegration contexts, i.e., alongsidestate-of-the-art silicon.As the industry progresses and thenearer-term Beyond CMOS candidatesbecome more central to the IRDS,the focus of logic device evaluationbeyond CMOS will evolve. Thoughthe core focus remains on digital information processing, it seems lessand less likely that a candidate willemerge that will take over the mantleof the silicon FET as the workhorse oflinear, multi-generational progressionfor the industry. Instead, a variety ofdevices tailored to a variety of applications and accelerators will need to beexplored and matured using ultimatesilicon as a foundation for experimentation and commercialization.IV. Emerging Architecturesand Device InteractionMany new emerging devices will require co-design between devices andhigher levels of computer design (e.g.,circuit, architecture, and application).These emerging devices are not intended simply as “drop-in” replace-ments for standard CMOS devices,but will require new types of circuit designs, new functional module architectures, and even new software to bestutilize the new devices’ capabilities [5].Novel design issues that span thedevice and architecture levels especially need to be considered whenadopting new low-level computingparadigms. Devices may be organized in radically new ways to carryout computation in a very differentstyle from what we may consider themost “conventional” computing paradigm, which has relied on standardcombinational and sequential nonreversible Boolean logic. The BeyondCMOS roadmap has begun trackingsome of the most common buildingblocks for emerging systems and applications as shown in Fig 3.At the device level, there are manytypes of devices that function as a synaptic device that both hold a storedstate and use that state to modulatean analog input. This type of deviceis critical to overcoming the von Neumann Bottleneck: rather than movingdata between memory and a processor, processing is directly integratedwith each memory element. The analog processing of a synaptic devicecan also replace the 1,000’s of transistors needed to do a digital operationwith a single device. Another important class of devices are stochasticdevices that generate a random binary or analog value. For many of thedevices the probability distribution istunable allowing for controllable randomness. Conventional digital logicis deterministic and cannot introducetrue randomness, and instead requirerelatively expensive pseudo randomnumber generators (PRNGs). Replacing a large expensive PRNG with asingle device allows one to consideralgorithms that are inherently stochastic and would otherwise be computationally expensive.At the circuit level there are bothcircuits dedicated to computing aspecific “neuron” function very efficiently, and circuits that are based ona crossbar array of synaptic devicesJuly 2021 IEEE Electron Devices Society Newsletter5

Figure 3. Emerging architectures require co-designing new devices, computational kernels and computational systems.Some of the possible building blocks are shown.to compute a given matrix operation.Converting between analog and digital is typically a very expensive operation, and so neuron devices andcircuits that can directly operate on ananalog input avoid this cost. Commonfunctions include leaky-integrate-andfire neurons, stochastic spiking neurons, rectified linear neurons, andsigmoidal neurons. At the array level,there are computational kernels thatcan read a matrix in parallel by performing matrix vector multiplication,write a matrix in parallel by updating all values by the outer productof two input vectors, approximatelysolve the matrix equation Ax b fora vector x, implement a content addressable memory, and provide areconfigurable analog computingsubstrate through a field programmable analog array.These enabling devices and circuitscan then be used to build a wide variety of architectures and systems.Neuro-inspired systems include conventional neural network inferenceand backpropagation based training.Spiking neural networks promise toreduce communication and analog todigital conversion (ADC) costs. Newneural training algorithms based on6local learning rules promise to drastically reduce the data-movement andbuffering needed to train a neural network. Hyperdimensional computing isa new high-dimensional learning system that is enabled by large hardwarebased content addressable memories.Dynamical systems can use thetemporal evolution of a recurrentlyconnected system to solve a variety ofproblems. Coupled oscillators can beused to solve optimization problems.Associative memories can be storedin Hopfield networks. Differentialequations can be mapped to analogsubstrates, and reservoir computingsystems can be used to analyze temporal data. Chaotic logic networks cancarry out monolithic reversible transformations of the state of a Boolean circuit even down to sub-kT signal levels.Stochastic devices enable new systems that are built around repeatedrandom sampling. Simulated annealing can be used to solve optimizationproblems. Stochastic devices enableMonte Carlo simulation. True randomnumber generation is critical for cryptographic applications and tunable random devices enable probabilistic logic.In addition to developing accelerators for specific computing functions,IEEE Electron Devices Society Newsletter July 2021reversible computing systems aim tolower the energy dissipation of general digital logic, including both general-purpose programmable digitalprocessors, and more specialized digital ASICs. Rigorous thermodynamicarguments have shown that the fundamental Landauer limit on energyefficiency can only be avoided in deterministic computational processescomposed from local primitive operations if they have the property of(conditioned or unconditional) logicalreversibility [6]. In addition to the potential for reducing minimum energydissipation below conventional limits,reversible techniques can potentiallyexceed the conventional limits onlarger-scale practical computing efficiency. Concrete examples of reversible computing systems based onboth semiconducting and superconducting technology platforms havebeen demonstrated, and this areaseems ripe for further development.In this section, the Beyond CMOSroadmap has surveyed a variety ofconcepts and R&D directions for thedevelopment of novel beyond-CMOScomputing technologies that represent an effort to think “outside thebox,” in the sense of looking beyond

just developing simple drop-in replacements for traditional logic andmemory cells. More broadly, newhardware designs spanning multiplelevels from the devices up throughcircuits and architectures must beconsidered, and the interactions between the various levels explored.More specifically, we expand thescope of future computing technologies beyond traditional irreversible,deterministic digital logic to include abroad range of alternative, unconventional computational paradigms, suchas analog, probabilistic, and (classical) reversible computing paradigms.V. Emerging MaterialsIntegrationIn the previous ITRS activities thatform integrated knowledge and collective intelligence in academia,consortia, and industry researchers,the international technology working group of Emerging ResearchMaterials (ERM) presented potentialsolutions from a materials scienceperspective for future logic and memory devices, front end processing, interconnects, assembly and package,lithography, metrology, and life-cycleassessment of Environment, Safety,and Health (ESH)-related issues [7].Taking over that experience, the IRDS2020 edition set up “Emerging Materials Integration (EMI)” section inthe “Beyond CMOS” chapter. Whileexisting technologies are integratedon a Si-based platform, the majority of beyond-CMOS technologiesare based on entirely new materialsand cutting-edge material science.The key EMI challenge is to providetimely guidance on emerging materials, process performance, cost,reliability, and sustainable developments that will drive breakthroughsin the future. Figure 4 depicts the roleof EMI, which is to promote the advancement of existing technologies.The current EMI section emphasizes strategic challenges, novel breakthroughs, and potentially disruptiveopportunities for emerging materialproperties, synthetic methods, andFigure 4. Emerging Material Integration promotes the advancement of existing technologies.metrology, organized in the followingareas: (1) Scaled technology materials needs for More Moore, (2) Novelmaterials for Beyond CMOS, and (3)Potentially disruptive material opportunities for functional scaling andconvergent applications. Regardingmaterials for advanced More Mooretechnologies, high mobility transitionmetal dichalcogenides (TMD) withlow defect density and low resistanceohmic contacts are listed as a longterm difficult challenge. Nano-carbonmaterials, complex metal oxides andspin-related materials are attractingattention as materials for non-CMOSlogic and memory devices. Novelinterlayer dielectrics, such as MetalOrganic Framework (MOF) and Carbon Organic Framework (COF) willimprove the interconnect reliability.Materials and processes that enablemonolithically 3D integrated complex functionality, such as integrationwith flexible electronics and biocompatible functional materials, are alsoincluded in long-term challenges. Asone of the convergent opportunities,EMI section refers to Big data andDigital transformation

memory and logic devices, the BC chapter has placed significant emphasis on emerging device-architecture interactions. JULY 2021 VOL. 28, NO. 3 ISSN: 1074 1879 EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI . Email: jmolina@inaoep.mx Latin America South (Region 9) Paula Ghedini Der Agopian UNESP, Sao Paulo State University Email: paula.agopian@unesp.br .