Transcription

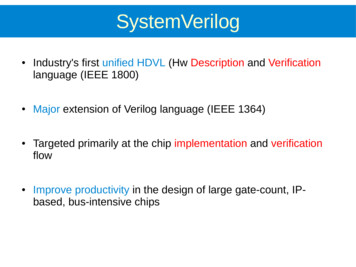

Push-Button EngineeringandSystemVerilogStuart SutherlandPresidentSutherland HDL, Inc.Training engineersto be HDL wizardswww.sutherland-hdl.com

About the Presenter. Stuart Sutherland SystemVerilog design and verification consultantx Involved in hardware design since 1982x Have been using Verilog since 1988x Specializes in providing Verilog/SystemVerilog trainingx Bachelors degree in Computer Science with an emphasisin Electronic Engineeringx Pursuing a Master’s degree in education Member of the IEEE Verilog and SystemVerilog standardsgroups since 1993x Editor of IEEE 1364 Verilog and IEEE 1800 SystemVerilogLanguage Reference Manuals (LRMs)x Author of multiple books on Verilog and SystemVerilogPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.2

Push Button Engineering “Electronic Design Automation” means: I think about what I want a new design to do I sketch the design idea on a napkin I scan in the napkin and push a button A software program transforms the ideas into a fullyworking, verified netlist ready to implement in silicon! Do we have push button engineering today? Do we even want push push button engineeing?Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.3

Yes! Yes, we do want push button engineering Design automation makes engineering easier Design automation enables engineers to do bigger designs Design automation does not eliminate engineering jobsx It eliminates the mundane work so we can be creative! Yes, we really do have push button engineering today How did we design in the 1960s, 1970s, and 1980s? Drafting was “automated” with schematic capture tools Gate-level design was automated with RTL synthesis SystemVerilog is a new level of push button engineering!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.4

designverificationSystemVerilog is theNext Evolution of VerilogSystemVerilog-2005assertionstest program blocksclocking domainsprocess controlmailboxessemaphoresconstrained random valuesdirect C function callsclassesinheritancestringsdynamic arraysassociative arraysreferencesinterfacesnested hierarchyunrestricted portsautomatic port connectenhanced literalstime values and unitsspecialized procedurespackages2-state modelingpacked arraysarray assignmentsqueuesunique/priority case/ifcompilation unit inuereturndo–while -- - * / & % Verilog-2001 / Verilog-2005ANSI C style portsgeneratelocalparamconstant functionsstandard file I/O value plusargs ifndef elsif line@*(* attributes *)configurationsmemory part selectsvariable part selectmulti dimensional arrayssigned typesautomatic** (power operator)Verilog-1984 (IEEE Verilog-1995)modulesparametersfunction/tasksalways @assign finish fopen fclose display write monitor define ifdef else include timescaleinitialdisableeventswait # @fork–joinwire reginteger realtimepacked arrays2D memorybegin–endwhilefor foreverif–elserepeatPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc. * /% 5

Top-10 Reasons EngineersLove SystemVerilog Abstract modeling enhancements1) Abstract data types2) Non-ambiguous procedures3) New programming statements and operators4) Enhanced tasks and functionsMoreMore functionalityfunctionality5) Simplified netlists and interfacesinin fewerfewer lineslines ofof code!code! Powerful verification enhancements1) Assertions2) Race-free testbench/design communication3) Object-oriented types and techniques4) Constrained random tests and coverage5) Direct programming interface (DPI)MoreMore testingtestinginin fewerfewer lineslines ofof code!code!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.6

Top 5 ModelingEnhancements1) Abstract data types99999High-level data typesRelaxed rules on data type usageEnumerated typesUser-defined typesStructuresMoreMore functionalityfunctionalityinin fewerfewer lineslines ofof code!code!2) Non-ambiguous procedures3) New programming statements and operators4) Enhanced tasks and functions5) Simplified netlists and interfacesPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.7

SystemVerilog RelaxesVariable Restrictions Verilog has strict rules on when to use a variable (e.g.reg) and when to use a net (e.g. wire) Context dependent A variable cannot be “driven” by a continuousassignment or an output port SystemVerilog allows variables to be used in the sameplaces a net can be used: Simplifies writing models Can evolve from algorithmic to behavioral to RTLto gate without changing data types Limited to a single driverx Prevents unintentional shared variable behaviorPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.8

Enumerated Types Verilog does not have enumerated types Regular variables must be used for state machines, etc.x Must specify actual logic values in modelsx Cannot limit values to a legal set SystemVerilog adds enumerated types, using enum Allows modeling at a more abstract level Strongly typed — prevents many common coding errorsenumenum {WAIT,{WAIT, LOAD,LOAD, READY}READY} state;state;alwaysalways @(state@(state oror opcode)opcode)casecase (state)(state)WAIT:WAIT: next statenext state LOAD;LOAD;. Can specify hardware implementation details (e.g. 1-hot)enumenum bitbit [3:0][3:0] {WAIT 3’b001,{WAIT 3’b001, LOAD 3’b010,LOAD 3’b010, READY 3’b100}READY 3’b100} state;state;Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.9

Structures SystemVerilog adds C-like structures to VerilogAA structurestructure isis aa collectioncollection ofof elementselements thatthat cancan bebe differentdifferent typestypes andand sizessizes Can be used to bundle several variables into one object Can assign to individual signals within the structure Can assign to the structure as a whole Can pass structures through ports and to tasks or functionsTheThe structurestructure declarationdeclarationstruct{struct {syntaxsyntax isis similarsimilar toto CCinti0,i1;int i0, i1;bitbit [7:0][7:0] opcode;opcode;}} instruction word;instruction word;.instruction wordinstruction word {56,15,8’hF1};{56,15,8’hF1};Now I can work with wholeblocks of data as one object!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.10

Top 5 ModelingEnhancements1) Abstract data types2) Non-ambiguous procedures99Hardware specific proceduresUnique and priority decisionsMoreMore functionalityfunctionalityinin fewerfewer lineslines ofof code!code!3) New programming statements and operators4) Enhanced tasks and functions5) Simplified netlists and interfacesPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.11

Inferring HardwareFrom always Procedures Verilog’s always procedure is a general purpose codingprocedure Used to model combinational logic, latched logic, sequentiallogic, bus-functional logic, and testbench logic Software tools must “infer” (guess ) what type of hardwarean engineer intended based on contextalwaysalways @(posedge@(posedge clock)clock)beginbeginifif (mode)(mode) q1q1 aa bbelseq1elseq1 aa -- b;b;q2q2 q1q1 (q2 (q2 2);2);q2 ;q2 ;endendIsIs q1q1 combinationalcombinational logiclogicoror sequentialsequential logic?logic?DoesDoes q2q2 everever increment?increment?Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.1212

Hardware SpecificProcedures SystemVerilog adds hardware-oriented procedures always ff models sequential logic always comb models combinational logic always latch models latch-based logic These hardware-oriented procedures Allow software tools to check that designer’s intent hasbeen correctly modeled Require simulation, synthesis, and formal tools to use thesame rulesalways combalways combifif (!mode)(!mode)yy aa b;b;elseelseyy aa -- b;b;nono sensitivitysensitivity listlistcontentscontents mustmust followfollow synthesissynthesis rulesrulesToolsTools nownow knowknow thethe designer’sdesigner’s intent,intent, andand cancan verifyverifythatthat thethe codecode modelsmodels combinationalcombinational behaviorbehaviorPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.13

Unique and PriorityDecisions Verilog defines that case decisions statements executewith priority encoding In simulation, only the first matching branch is executed “full case” and “parallel case pagmas are used to tellsynthesis to optimizex Simulation does not check that these pragmas will work! SystemVerilog adds unique and priority modifiers: Works like the pragmas for synthesis Simulation will warn if decision statements do not match thespecified behaviorAutomaticallyAutomaticallycatchescatches designdesign errorserrorsuniqueunique case(state)case(state)red:ifred:if (sensor(sensor 1)1) next statenext state green;green;yellow:yellow: ifif (yellow downcnt(yellow downcnt 0)0) next statenext state red;red;green:green: ifif (green downcnt(green downcnt 0)0) next statenext state yellow;yellow;endcaseendcasePush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.14

Top 5 ModelingEnhancements1) Abstract data types2) Non-ambiguous procedures3) New programming statements and operators9999Increment and decrement operatorsAssignment operatorsEnhanced for-loopsNew types of loops4) Enhanced tasks and functions5) Simplified netlists and interfacesMoreMore functionalityfunctionalityinin fewerfewer lineslines ofof code!code!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.15

Enhanced For-Loops In Verilog for loops The loop control variable be declared outside of the loopintegerinteger i;i;alwaysalways @(a@(a oror b)b)forfor (i(i 0;0; ii 255;255; ii ii 1)1).alwaysalways @(posedge@(posedge clock)clock)for(i 0;i for (i 0; i 255;255; ii ii 1)1).TheThe declarationdeclaration andandusageusage cancan separatedseparated bybymanymany lineslines ofof codecodeConcurrentConcurrent loopsloops cancaninterfereinterfere withwith eacheach otherother SystemVerilog enhances for loops The loop variable can be declared in the for loop Can have multiple initial and step assignmentsalwaysalways @(a@(a oror b)b)LoopLoop variablevariable isis declareddeclaredfor(inti for (int i 0;0; ii 255;255; i )i )locallocal toto thethe looploop.alwaysalways @(posedge@(posedge clock)clock)ConcurrentConcurrent loopsloops cannotcannotforfor (int(int ii 0,0, jj 255;255; ii 255;255; i ,i , j--)j--)interfereinterfere.Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.16

New Types of Loops Verilog has for, repeat and while loops The control is tested at the beginning of each loop pass SystemVerilog adds a do—while loop The control is tested at the end of each pass of the loopdodothethe looploop willwill executeexecute atat leastleast once,once, settingsetting donedone andand OutOfBoundOutOfBound flagflagbeginbegindonedone 1;1; OutOfBoundOutOfBound 1;1;if(addrdoneif(addr 0)0)done 1;1;elseelse ifif (addr(addr 255)255) OutOfBoundOutOfBound 1;1;elsebeginout mem[addr];elsebegin out mem[addr]; addraddr - - 8;8; endendendendwhilewhile (addr(addr -9-9 addraddr 255)255) SystemVerilog adds a foreach loop Iterates through arrays of any size and number of dimensionsint array1 [0:7][0:255];foreach ( array1 [i,j] ) display("i %d j %d array1[i][j] %d", i, j, array1[i][j]);Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.17

Top 5 ModelingEnhancements1) Abstract data types2) Non-ambiguous procedures3) New programming statements and operators4) Enhanced tasks and functions99999C-like function returnsDefault data types for formal argumentsPassing arrays and structures as argumentsPassing arguments by namePassing arguments by reference5) Simplified netlists and interfacesMoreMore functionalityfunctionalityinin fewerfewer lineslines ofof code!code!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.18

Task/Function Arguments:Passing By Name In Verilog: Values are passed to tasks and functions by positionHow can I know if stack and data bus are in the right order?always @(posedge clock)result subtractor( stack, data bus );function integer subtractor(input integer a, b);subtractor a - b;endfunction In SystemVerilog: Values can be passed using the formal argument namealways @(posedge clock)result subtractor( .b(stack), .a(data bus) );function int subtractor(int a, b);return(a - b);endfunctionUsesUses samesame syntaxsyntax asas namednamedmodulemodule portport connectionsconnectionsPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.19

Task/Function Arguments:Pass By Reference With Verilog tasks and functions: Input values are copied in — outputs are copied out[always[always @(posedge@(posedge clock)clock)resultresult mult(mult( data,data, stack[14]stack[14] ););datadata andand stackstack areare copiedcopied intointothethe functionfunction whenwhen itit isis calledcalledfunctionfunction integerinteger mult(inputmult(input [31:0][31:0] a,a, b);b);. With SystemVerilog: Tasks and functions can “reference” the calling argumentsx Uses the keyword ref instead of input, output or inoutalwaysalways @(data)@(data)synchsynch (data,(data, clock);clock);tasktask synchsynch (int(int d,d, refref clk);clk);@(posedge@(posedge clk)clk) //sync//sync toto clockclock.TheThe tasktask isis sensitivesensitive toto changeschangesonon clockclock inin thethe callingcalling scopescopebitbit [31:0][31:0] stackstack [0:255];[0:255];alwaysalways @(posedge@(posedge clock)clock)resultresult mult(mult( data,data, stackstack ););functionfunction intint mult(intmult(int a,a, refref b);b);.TheThe functionfunction directlydirectly referencesreferencesstackstack inin thethe callingcalling scopescopePush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.20

Top 5 ModelingEnhancements1) Abstract data types2) Non-ambiguous procedures3) New programming statements and operators4) Enhanced tasks and functions5) Simplified netlists and interfaces999Relaxed port connection rulesAutomatic netlist connectionsInterfacesMoreMore functionalityfunctionalityinin fewerfewer lineslines ofof code!code!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.21

Module Port Connections Verilog restricts the data types that can beconnected to module ports Only net types on the receiving side Nets, regs or integers on the driving side Choosing the correct type frustrates Verilog modelers SystemVerilog removes restrictions on port connections Any data type on either side of the port Real numbers (floating point) can passthrough ports Arrays can be passed through ports Structures can be passed through portsPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.22

Module Port ConnectionShortcuts Verilog module instances can use port-name connections Must name both the port and the net connected to itmodulemodule dffdff (output(output q,q, qb,qb,inputinput clk,clk, d,d, rst,rst, pre);pre);cancan bebe verboseverbose andand ip(output[3:0]q,endmoduleendmoduleinputinput [3:0][3:0] d,d, inputinput clk,clk, rst,rst, pre);pre);dffdff dff1dff1 (.clk(clk),(.clk(clk), .rst(rst),.rst(rst), .pre(pre),.pre(pre), .d(d[0]),.d(d[0]), .q(q[0]));.q(q[0]));. SystemVerilog adds .name and .* shortcuts .name connects a port to a net of the same namedffdffdff1dff1 (.clk,(.clk, .rst,.rst, .pre,.pre, .d(d[0]),.d(d[0]), .q(q[0]));.q(q[0])); .* automatically connects all ports and nets with the samenamedffdffdff1dff1 (.*,(.*, .q(q[0]),.q(q[0]), .d(d[0]));.d(d[0]));Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.23

Interfaces:Communication Channels Verilog connects models using detailed module portsWhite BoardVerilog ModelsConnectionsConnections mustmust bebe modeledmodeledatat implementationimplementation levellevelInterconnectionInterconnection detailsdetails mustmustbebe duplicatedduplicated inin everyevery modulemodule SystemVerilog adds compound “interface” portsWhite BoardVerilog ModelsConnectionsConnections betweenbetweenmodulesmodules areare bundledbundled togethertogetherModulesModules useuse simplesimple ports,ports, ananinterfaceinterface bundlebundlePush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.24

InterfacesCan Contain Logic SystemVerilog interfaces are more than a bundle of wires Interfaces can contain declarationsx Variables, parameters and other data that is shared by allusers of an interface can be declared in one location Interfaces can contain tasks and functions (“methods”)x Operations shared by multiple connections to theinterface can be coded in one place Interfaces can contain proceduresx Protocol checking and other verification can be built intothe interfacePush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.25

Top 5 VerificationEnhancements1) Assertions9999Clocked sequential assertionsUnified assertions with PSLAssertions for design engineersAssertions for verification engineersMoreMore testingtestinginin fewerfewer lineslines ofof code!code!2) Race free testbench / design communications3) Object Oriented test programming4) Constrained random tests and functional coverage5) Direct Programming InterfacePush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.26

Assertions An assertion is a design condition that must be true Assertions can be written in Verilog, but It’s a lot of code!012345reqackEachEach requestrequest mustmust bebe followedfollowed byby ananacknowledgeacknowledge withinwithin 11 toto 33 clockclock cyclescyclesToTo testtest forfor aa sequencesequence ofof eventseventsrequiresseverallinesofVerilogrequires several lines of Verilog codecode DifficultDifficult toto write,write, readread andand maintainmaintain CannotCannot easilyeasily bebe turnedturned offoff duringduringresetreset oror otherother don’tdon’t carecare timestimesalways @(posedge req) begin@(posedge clk) ; // synch to clockfork: watch for ackparameter N 3;begin: cycle counterrepeat (N) @(posedge clk); display("Assertion Failure", time);disable check ack;end // cycle counterbegin: check ack@(posedge ack) display("Assertion Success", time);disable cycle counter;end // check ackjoin: watch for ackendPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.27

SystemVerilog Assertions SystemVerilog adds assertion syntax and semantics Immediate assertions test for a condition at the current timegenerategenerate aa fatalfatal errorerrorifif resetreset isis truetrueandand notnot inin thethe resetreset statestatealwaysalways @(state)@(state)assertassert (reset(reset &&&& (state(state ! ! RST))RST)) elseelse fatal); fatal); Concurrent assertions test for a sequence of events spreadover time0aa complexcomplex sequencesequence cancan bebedefineddefined inin veryvery conciseconcise codecode12345reqacka reqack: assert property (@(posedge clk) req ##[1:3] ack;) else error;OneOne lineline ofof SVASVA codecode replacesreplaces allall thethe VerilogVerilog codecode inin thethe previousprevious example!example!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.28

Advantages ofSystemVerilog Assertions SystemVerilog Assertions have several advantages Concise syntax!x Many lines of Verilog code can be represented in one line Ignored by Synthesis!x Don’t have to hide Verilog checker code withinconvoluted translate off / translate on synthesis pragmas Can be disabled!x SystemVerilog assertions can be turned off during reset,or until simulation reaches a specific simulation time Can have severity levels!x SystemVerilog assertion failures can be non-fatal or fatalx Simulators can suppress messages based on severityPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.29

Assertions Are forDesign Engineers, Too Design engineers should write assertions to verifyassumptions that affect the functionality of a design block The assertion documents the designer’s assumptionsxExample: An ALU design assumes that the A, B and opcodeinputs will never have a logic X or Z value Verification engineers should write assertions that verify designfunctionality meets the overall design specification The assertion verifies that the designer correctly implementedthe specificationxExample: The zero flag output of the ALU block should only beset if the ALU result output is zeroPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.30

Top 5 VerificationEnhancements1) Assertions2) Race free testbench / design communications999Enhanced schedulingProgram blockClocking domain3) Object Oriented test programmingMoreMore testingtestinginin fewerfewer lineslines ofof code!code!4) Constrained random tests and functional coverage5) Direct Programming InterfacePush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.31

Special Test Bench“Program Blocks” Verilog uses hardware modules to model the test bench No special semantics to avoid race conditions with thedesign SystemVerilog adds a special “program block” for testing Identifies verification code Program events are automatically synchronized to hardwareevents to avoid racesprogram test (input clk, input [15:0] addr, inout [7:0] data);initial begin@(negedge clk) data 8’hC4;address 16’h0004;@(posedge clk) verify results;endtask verify results;TheThe testbenchtestbench isis calledcalled aa “program“program block”block” becausebecause.testtest codecode isis moremore likelike softwaresoftware thanthan hardwarehardwareendprogramPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.32

Cycle-BasedVerification Timing Verilog has no special clock semantics for verification Must write extra code to avoid race conditions with design SystemVerilog adds a special “clocking domain” construct Specifies a test “input skew” and “output skew”x Offsets verification events are from the design clockclockingclocking busbus @(posedge@(posedge clock);clock);defaultdefault inputinput #2ns#2ns outputoutput #1ns;#1ns;inputenable,inputenable, full;full;inoutdata;inoutdata;outputoutput empty;empty;outputoutput #6ns#6ns reset;reset;endclockingendclockingsample heredrive hereinputoutputclockinput skewoutput skewdesign’s clock edgeInputInput skewskew isis howhow longlong beforebefore aa clockclock edgeedge aa valuevalue shouldshould bebe sampledsampled TheThe defaultdefault isis 1step1step (one(one simulationsimulation timetime unit)unit)OutputOutput skewskew isis howhow longlong afterafter thethe clockclock edgeedge beforebefore aa valuevalue shouldshould bebe drivendriven TheThe defaultdefault isis 00Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.33

Top 5 VerificationEnhancements1) Assertions2) Race free testbench / design communications3) Object Oriented test programming99999ClassesInheritancePolymorphismData hiding and protectionMailboxes and semaphoresMoreMore testingtestinginin fewerfewer lineslines ofof code!code!4) Constrained random tests and functional coverage5) Direct Programming InterfacePush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.34

Object Oriented Classes SystemVerilog adds “classes” to the Verilog language Allows Object Oriented Programming techniques Class definitions can containx Data declarationsclassclass PacketPacket ;;randrand bit[3:0]bit[3:0] cmd;cmd;(“properties”)localstatus;local intintstatus;myStructheader;x Tasks and functionsmyStructheader;constraintconstraint c1c1 {{ cmd[0]cmd[0] 1’b0;1’b0;(“methods”)functionfunction intint get status();get status();. Similar to C and VERA:endfunctionendfunctionx Can have inheritance andtasktask set cmd(inputset cmd(input bitbit a);a);.polymorphismendtaskendtaskx Can have public, local or endclassendclassprivate data encapsulation classclass udpPacketudpPacket extendsextends PacketPacket ;;.x Automatic garbageendclassendclasscollectionPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.}}35

Enhanced Synchronization:Mailboxes and Semaphores SystemVerilog has built-in classes to synchronize tests Semaphoresx Represents a bucket with a fixed number of keysx Class methods are used to check keys in and outx If keys are available, a process suspends executionand waits for keys before continuing Mailboxesx Represents a FIFO to exchange messagesxxbetween processesClass methods allow adding a message orretrieving a messageIf no message is available, a process can either wait untila message is added, or continue and check again laterPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.36

Top 5 VerificationEnhancements1) Assertions2) Race free testbench / design communications3) Object Oriented test programming4) Constrained random tests and functional coverage99999Distributed random valuesCyclic random valuesConstrained random valuesSeparate RNG for each objectFunctional coverage5) Direct Programming InterfaceMoreMore testingtestinginin fewerfewer lineslines ofof code!code!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.37

Enhanced Random Values Verilog random returns a 32-bit signed random number Cannot constrain the random values returned SystemVerilog adds constrained random values rand — distributed random numbers randc — cyclic random numbersTheThe variablesvariables toto receivereceive randomrandom values,values, andand anyanyclassclass Bus;Bus;constraints onon thethe randomrandom values,values, areare specifiedspecified usingusingrandrand bitbit [15:0][15:0] addr;addr; constraintsclassrandclass objectsobjects andand classclass methodsmethodsrand bitbit [31:0][31:0] data;data;randcrandc bitbit [3:0][3:0] mode;mode;constraintconstraint word alignword align {addr[1:0]{addr[1:0] 2’b0;}2’b0;}endclassendclassBusBus busbus new;new;repeatrepeat (50)(50)GenerateGenerate 5050 randomrandom valuesvalues forfor thethe variablesvariables inin thethe “bus”“bus” objectobjectbeginbeginassertassert g randomize()randomize() selectsselects valuesvalues forfor allall randomrandom variablesvariablesinin aa classclass object,object, usingusing thethe constraintsconstraints specifiedspecifiedPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.38

Functional Coverage SystemVerilog functional coverage provides: User specified cover groups (encapsulates coverage models)x Cover pointsx Variables and expressions to be trackedx Cover binsx Values or value ranges to be trackedx Cross coveragex Value sets received by multiple cover pointsenum {WAIT, LOAD, READY} state, next state;logic [7:0] data;covergroup cg state coverage @(posedge clk);states: coverpoint state;values: coverpoint data {bins low { [0:127] };bins high { [128:255] };}endgroupPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.39

Top 5 VerificationEnhancements1) Assertions2) Race free testbench / design communications3) Object Oriented test programming4) Constrained random tests and functional coverage5) Direct Programming Interface999A simplified complement to the Verilog PLIVerilog can directly call C functionsC functions can directly call VerilogfunctionsMoreMore testingtestinginin fewerfewer lineslines ofof code!code!Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.40

DirectProgramming Interface Verilog uses the Programming Language Interface (PLI) toallow Verilog code to call C language code Powerful capabilities — traversing hierarchy, controllingsimulation, modifying delays and time synchronization Difficult to learn Too complex for many types of applications SystemVerilog adds a Direct Programming Interface (DPI) Verilog code can directly call C functions C functions can directly call Verilog functions Can do many things more easily than the PLIx Cannot do everything the PLI can do Ideal for interfacing to bus-functional models written in CPush Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.41

SystemVerilog Adds a NewLevel of Push Button Engineering Modeling enhancements enable engineers to modellarger designs and avoid common design errors Abstract data types Non-ambiguous procedures New programming statements and operators Enhanced tasks and functions Simplified netlists and interfaces Powerful verification enhancements enable verifyingcomplex designs more effeciently and effectively Assertions Race-free testbench/DUT communication Object-oriented types and techniques Constrained random test and coverage Direct Programming Interface (DPI)Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc.42

Push Button Engineering and SystemVerilog — 2008, Sutherland HDL, Inc. 3 Push Button Engineering “Electronic Design Automation”means: I think about what I want a new design to do I sketch the design idea on a napkin I scan in the napkin and push a button A software program transforms the ideas into a fully