Transcription

CMOSManufacturingProcessDigital Integrated CircuitsManufacturing ProcessEE141

CMOS ProcessDigital Integrated CircuitsManufacturing ProcessEE141

A Modern CMOS Processgate-oxideTiSi2AlCuSiO2Tungstenpolyp-welln SiO2n-wellp-epip p Dual -Well Trench -Isolated CMOS ProcessDigital Integrated CircuitsManufacturing ProcessEE141

Circuit Under DesignVDDVDDM2M4VoutVinM1Vout2M3This two-inverter circuit (of Figure 3.25 in the text) will bemanufactured in a twin-well process.Digital Integrated CircuitsManufacturing ProcessEE141

Circuit LayoutDigital Integrated CircuitsManufacturing ProcessEE141

The Manufacturing ProcessFor a great tour through the process and its different steps, ductors.htmlFor a complete walk-through of the process (64 steps), check theBook okDigital Integrated CircuitsManufacturing ProcessEE141

Photo-Lithographic Processopticalmaskoxidationphotoresistremoval (ashing)photoresist coatingstepper exposureTypical operations in a singlephotolithographic cycle (from [Fullman]).photoresistdevelopmentacid etchprocessstepDigital Integrated Circuitsspin, rinse, dryManufacturing ProcessEE141

Patterning of SiO2Chemical or plasmaetchSi-substrateHardened resistSiO2(a) Silicon base materialSi-substratePhotoresistSiO2(d) After development and etching of resist,chemical or plasma etch of SiO2Si-substrateHardened resistSiO2(b) After oxidation and depositionof negative photoresistSi-substrateUV-lightPatternedoptical mask(e) After etchingExposed resistSi-substrate(c) Stepper exposureDigital Integrated CircuitsSiO2Si-substrate(f) Final result after removal of resistManufacturing ProcessEE141

CMOS Process at a GlanceDefine active areasEtch and fill trenchesImplant well regionsDeposit and patternpolysilicon layerImplant source and drainregions and substrate contactsCreate contact and via windowsDeposit and pattern metal layersDigital Integrated CircuitsManufacturing ProcessEE141

CMOS Process Walk-Throughp-epi(a) Base material: p substratewith p-epi layerp SiN34p-epiSiO2(b) After deposition of gate-oxide andsacrificial nitride (acts as abuffer layer)p (c) After plasma etch of insulatingtrenches using the inverse ofthe active area maskp Digital Integrated CircuitsManufacturing ProcessEE141

CMOS Process Walk-ThroughSiO2(d) After trench filling, CMPplanarization, and removal ofsacrificial nitridenpDigital Integrated Circuits(e) After n-well andVTp adjust implants(f) After p-well andVTn adjust implantsManufacturing ProcessEE141

CMOS Process Walk-Throughpoly(silicon)(g) After polysilicon depositionand etchn p (h) After n source/drain andp source/drain implants. Thesesteps also dope the polysilicon.SiO2(i) After deposition of SiO 2insulator and contact hole etch.Digital Integrated CircuitsManufacturing ProcessEE141

CMOS Process Walk-ThroughAl(j) After deposition andpatterning of first Al layer.AlSiO2(k) After deposition of SiOinsulator, etching of via’s, 2deposition and patterning ofsecond layer of Al.Digital Integrated CircuitsManufacturing ProcessEE141

Advanced MetalizationDigital Integrated CircuitsManufacturing ProcessEE141

Advanced MetalizationDigital Integrated CircuitsManufacturing ProcessEE141

Design RulesJan M. RabaeyDigital Integrated CircuitsManufacturing ProcessEE141

3D PerspectivePolysiliconDigital Integrated CircuitsManufacturing ProcessAluminumEE141

Design RuleslllInterface between designer and processengineerGuidelines for constructing process masksUnit dimension: Minimum line width» scalable design rules: lambda parameter» absolute dimensions (micron rules)Digital Integrated CircuitsManufacturing ProcessEE141

CMOS Process LayersLayerColorWell (p,n)YellowActive Area (n ,p )GreenSelect (p ,n )GreenPolysiliconRedMetal1BlueMetal2MagentaContact To PolyBlackContact To DiffusionBlackViaBlackDigital Integrated CircuitsManufacturing ProcessRepresentationEE141

Layers in 0.25 µm CMOS processDigital Integrated CircuitsManufacturing ProcessEE141

Intra-Layer Design RulesSame Potential0or6WellDifferent Potential29Polysilicon2103ActiveContactor ViaHole323Metal1232Select4Metal23Digital Integrated CircuitsManufacturing ProcessEE141

TransistorTransistor Layout1325Digital Integrated CircuitsManufacturing ProcessEE141

Vias and Contacts24Via115Metal to1Active ContactMetal toPoly Contact3222Digital Integrated CircuitsManufacturing ProcessEE141

Select Layer2Select3213325WellSubstrateDigital Integrated CircuitsManufacturing ProcessEE141

CMOS Inverter LayoutInGNDVD DAA’Out(a) LayoutAA’np-substraten p FieldOxide(b) Cross-Section along A-A’Digital Integrated CircuitsManufacturing ProcessEE141

Layout EditorDigital Integrated CircuitsManufacturing ProcessEE141

Design Rule Checkerpoly not fet to all diff minimum spacing 0.14 um.Digital Integrated CircuitsManufacturing ProcessEE141

Sticks DiagramV DD3OutIn1 Dimensionless layout entities Only topology is important Final layout generated by“compaction” programGNDStick diagram of inverterDigital Integrated CircuitsManufacturing ProcessEE141

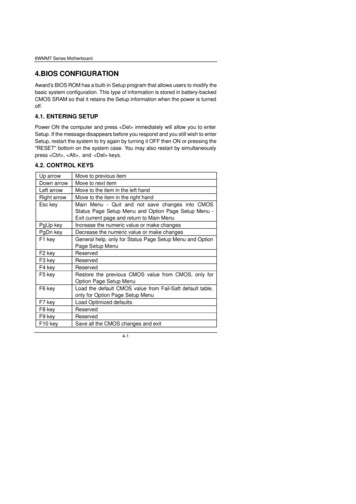

Book web-page. Digital Integrated Circuits Manufacturing Process EE141 oxidation optical mask process step photoresist photoresist coating removal (ashing) . Digital Integrated Circuits Manufacturing Process EE141 CMOS Process at a Glance Define active areas Etch and fill trenches I