Transcription

Alveo Data CenterAccelerator Card PlatformsUser GuideUG1120 (v1.4) April 26, 2021

Revision HistoryRevision HistoryThe following table shows the revision history for this document.Revision SummarySection04/26/2021 Version 1.4Chapter 5: Alveo PlatformsUpdated available platforms. Chapter 4: Platform FeaturesAdded: U250 Gen3x16 XDMA 2 1 PlatformSlave-bridge (SB) feature renamed to host memory (HM). Added: Gigabit Transceiver (GT)Updated: Slave-bridge (SB) renamed to host memory(HM).Chapter 5: Alveo PlatformsUnder Tool Support, removed 2021.2 column.Alveo PCIe InformationReplaced content with link to Appendix A in the Alveo CardOut-of-Band Management Specification for Server BMCdocumentation, which provides the same information.U250 Gen3x16 XDMA 3 1 PlatformAdded target card: A-U250-P64G-PQ-GUpdated the descriptions for OS Version, removing as theopener to this block from the first sentence: Only present forUbuntu packages (as the opener to this block).01/13/2021 Version 1.3Chapter 4: Platform FeaturesTwo feature descriptions added: host memory transfers anddynamic function eXchange technologyPackage Naming Convention 2020.1 Release and LaterUpdated information for operating systems, where newpackages will support all Ubuntu releases.Chapter 5: Alveo PlatformsUpdated available platforms. Removed: U50 XDMA 201920 1 PlatformU50 XDMA 201910 1 PlatformU200 XDMA 201830 1 PlatformU250 XDMA 201830 1 PlatformU250 Gen3x16 XDMA 3 1 PlatformU280 XDMA 201920 2 PlatformU280 XDMA 201920 1 PlatformU280 XDMA 201910 1 PlatformAdded: U250 Gen3x16 XDMA 3 1 PlatformAlveo PCIe InformationNew topic capturing PCIe information for Alveo U200, U250,U280, and U50 cards.U50 Gen3x4 XDMA base 2 PlatformUpdated values.U50 Gen3x16 XDMA 201920 3 PlatformUpdated values.U200 XDMA 201830 2 PlatformUpdated values.U250 XDMA 201830 2 PlatformUpdated values.U250 Gen3x16 XDMA 3 1 PlatformAdded platform.UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com2

Revision HistorySectionRevision SummaryU280 XDMA 201920 3 PlatformUpdated card shutdown description with regard to thesatellite controller.Updated values.6/26/2020 Version 1.2Chapter 3: Platform Naming and Life CycleUpdated section to delineate between the platform releasesprior to 2020.1 and the 2020.1 release.Chapter 5: Alveo PlatformsUpdated release notes and target card information in eachplatform section.U50 Gen3x4 XDMA base 2 PlatformAdded platform information.U50LV Gen3x4 XDMA base 2 PlatformAdded platform information.U50 Gen3x16 XDMA 201920 3 PlatformAdded Vitis tools 2020.1 support.U200 XDMA 201830 2 PlatformU250 XDMA 201830 2 PlatformU280 XDMA 201920 3 Platform4/22/2020 Version 1.1Table 8: xilinx u50 gen3x16 xdma 201920 3 PlatformResource Availability Per SLRChanged the title from xilinx u50 xdma 201920 2 toxilinx u50 gen3x16 xdma 201920 3.Table 9: Available Memory Resources per SLRChanged the platform name in Note 1 fromxilinx u50 xdma 201920 2 toxilinx u50 gen3x16 xdma 201920 3.Table 10: xilinx u50 gen3x16 xdma 201920 3 DeploymentPlatform Installation Download LinksChanged the download links.U50 XDMA 201920 1 PlatformChanged heading title from U50 XDMA 201920 2 Platform toU50 XDMA 201920 1 Platform.U50 XDMA 201910 1 PlatformChanged heading title from U50 XDMA 201920 1 Platform toU50 XDMA 201910 1 Platform.3/10/2020 Version 1.0.1GeneralUpdated links throughout document.2/29/2020 Version 1.0Initial release.UG1120 (v1.4) April 26, 2021Alveo PlatformsThe Available Platforms section removed from the VitisUnified Software Platform Documentation: ApplicationAcceleration Development (UG1393).Added the xilinx u50 gen3x16 xdma 201920 3 andxilinx u280 xdma 201920 3 platforms.Send Feedbackwww.xilinx.com3

Table of ContentsRevision History.2Chapter 1: Overview.5Chapter 2: DMA Configurations.7Chapter 3: Platform Naming and Life Cycle. 8Package Naming Convention 2020.1 Release and Later. 8Platform Naming Convention Prior to 2020.1. 10Chapter 4: Platform Features. 12Chapter 5: Alveo Platforms. 13Alveo PCIe Information. 13U50 and U50LV.14U200. 20U250. 23U280. 32Appendix A: Additional Resources and Legal Notices. 36Xilinx Resources.36Documentation Navigator and Design Hubs.36References.36Please Read: Important Legal Notices. 37UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com4

Chapter 1: OverviewChapter 1OverviewXilinx Alveo Data Center accelerator cards are PCI Express compliant cards designed toaccelerate compute-intensive applications such as machine learning, data analytics, and videoprocessing in a server or workstation. The Vitis core development kit provides verified platformsdefining all the required hardware and software interfaces (shown in gray in the following figure),allowing you to design custom acceleration applications (shown in white) that are easilyintegrated into the Vitis programming model.Figure 1: Platform OverviewHost ServerAlveo DeviceApplicationKernelsAcceleration APIsAXI InterconnectRun Time LibrariesGlobal MemoryDriversDMA EngineUserApplicationCodePlatform(Hardware andSoftware)PCIeSoftware FrameworkHardware FrameworkX23444-012720On the Xilinx device, a platform consists of a static region and a dynamic region. The static regionof the platform provides the basic infrastructure for the card to communicate with the host andhardware support for the kernel. It includes the following features: Host Interface (HIF): PCIe endpoint to enable communication with external PCIe host Direct Memory Access (DMA): XDMA IP and AXI Protocol Firewall IPUG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com5

Chapter 1: Overview Clock, Reset, and Isolation (CRI): Basic clocking and reset for card bring-up and operation.Reset and Dynamic Function eXchange isolation structure are required for isolation duringpartial bitstream download. Card Management Peripheral (CMP): Peripherals responsible for board health and diagnostics,debug, and programming Card Management Controller (CMC): UART/I2C communication to satellite controller(MSP432), QSFP, sensors and manages firmware updates from the host (over PCIe) Embedded RunTime Scheduler (ERT): Schedule and monitor compute units during kernelexecutionFigure 2: Dynamic and Static Regions In a PlatformXilinx DeviceDynamic RegionCMPCMCERTHIFDMACRIStatic RegionX23445-012720Accelerated kernels go into the dynamic region. The features and resources available foraccelerated kernels are described in Chapter 5: Alveo Platforms.UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com6

Chapter 2: DMA ConfigurationsChapter 2DMA ConfigurationsDMA FeaturesXilinx provides a high-performance platform configuration to design custom accelerationapplications with XDMA.The XDMA platform, available on all Alveo accelerator cards provides: Memory-mapped DMA transfer High-bandwidth transfers Kernel support for memory-mapped AXI4Table 1: DMA Customization FeaturesFeatureXDMAHost interfaceGen3 x16 w/ 512-bit data pathData path512-bit wide memory-mapped AXI4DMA transactionsMemory-mapped transfers between on card DDR4/PLRAM memoriesMaximum transfer size256 MBDDR4 channelsU200/U250: 4x DDR4 16 GB (64 GB maximum)U280: 2x DDR4 16 GBUG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com7

Chapter 3: Platform Naming and Life CycleChapter 3Platform Naming and Life CyclePackage Naming Convention 2020.1 Releaseand LaterStarting with the 2020.1 release, Alveo platforms are delivered through three types of Linuxinstallation packages outlined in the following table.Table 2: Platform Installation Package TypesPackageDescriptionPartitionContains a device bitstream that implements part of the deployment platform in the Alveo card.ValidateContains code to validate a platform installation and Alveo card setup.FirmwareContains compiled SC and CMC firmware binary files.The following section describes the package naming convention for partition and validate types.They differ slightly from firmware.Partition and Validate Package NamingThe partition and validate installation package names are generated by concatenating thefollowing elements: name version - release - architecture [- OS version ]. extension Each element consists of one or more sub-elements and are further described in the followingtable.UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com8

Chapter 3: Platform Naming and Life CycleTable 3: Partition and Validate Package Element ExamplesVendor namexilinxCard nameu50u250ChassisConnectivity to the servergen3x16-xdmagen3x4-xdmaPartitionPartition name distinguishes the partition typeand can be one of base, shell or seReleaseArchitectureArchitectureVersion of chassis.Dot separated list of one or more integers.Increments when the corresponding chassisinterface changes.21.1Integer release number.2200000Indicates the architecture the package is builtfor.noarchallnoarch – No ArchitectureallOS VersionOS Version16.0418.04Only present for Ubuntu packages (as theopener to this block).Indicates supported Ubuntu version for somepackages.allNew packages will support all Ubuntu releasesand are denoted as all.ExtensionExtensionPackage file extensionRPMDEBThe following is an example of a deployment installation package for Ubuntu 16.04.xilinx-u50-gen3x4-xdma-base 2-2200000 all 16.04.debOnce a deployment partition package is installed, you can use XRT commands to display thepartition installed on the card. See xbmgmt Utility in the Application Acceleration Developmentflow of the Vitis Unified Software Platform Documentation (UG1416).Because the version number indicates compatibility with other partitions, the release number isnot displayed. The following is the displayed partition name for the example package.xilinx u50 gen3x4 xdma base 2Firmware Package NamingFirmware (SC and CMC) installation package names are generated by concatenating thefollowing elements: name - version - release - architecture [- OS version ]. extension UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com9

Chapter 3: Platform Naming and Life CycleEach element consists of one or more sub-elements as listed in the following table.Table 4: Firmware Package Element panyVendor nameProductFirmware product nameCardCard nameu250u50VersionVersionFirmware version number. Three integers joined bydots.1.0.134.3.9ReleaseReleaseCMC firmware uses an integer. SC firmware uses analpha-numeric number separated with a tes the architecture the package is built for.noarch – No ArchitectureOS VersionOS VersionOnly present for Ubuntu packages.Indicates the supported Ubuntu version for somepackages.xilinxcmcsc-fwnoarchallallNew packages will support all Ubuntu releases and aredenoted as all.ExtensionExtensionPackage file extension16.0418.04allRPMDEBThe following are examples of cmc and sc-fw package names:xilinx-cmc-u50 1.0.20-2853996 all 16.04.debxilinx-sc-fw-u50-5.0.27-2.e289be9 16.04.debPlatform Naming Convention Prior to 2020.1Platforms are delivered via standard RPM and DEB Linux installation packages. The packagename adheres to the nomenclature described in the following figure and provides the target cardname, any customized configurations, the major release version, and the minor release versions.For example, a platform for the U200 card with a main customization level XDMA that was builtusing the 2018.3 release might have a package name of xilinx u200 xdma 201830 2.UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com10

Chapter 3: Platform Naming and Life CycleFigure 3: Example of Package Namexilinx u200 xdma 201830 21120Package Naming ConventionsPackage names include the following information: company card customization major release minor release Company: Xilinx Card: Series name of the card. Customization: Significant platform feature set. In this case, XDMA is the availablecustomization. Major Release: Includes new features or capabilities. The six-digit number represents the Vitistool release (version) used to build the platform. The platform can work across multiple majorXRT and Vitis releases. Minor Release: Includes bug fixes and minor updates. Appends the major release with anothernumber.RECOMMENDED: Whenever possible, update to the latest release of a platform.Life-cycle of a PlatformPlatforms have at least one year of backward compatibility with XRT, but not more than two. If IPused in the dynamic region of the platform is auto-upgraded for the same time frame, thengenerally: A platform generated from a release that has major revision of tools/run time such as 2019.1is backward compatible until the last release of 2020 (2020.2). A platform generated from a release that has minor revision of tools/run time such as 2019.2is also backward compatible until the last release of 2020 (2020.2).Note: Xilinx reserves the right to make a backward incompatible change once a year with a major revision ofXRT, a platform, or the Vitis core development kit. Major revision changes are usually done in the firstrelease of a calendar year.UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com11

Chapter 4: Platform FeaturesChapter 4Platform FeaturesDifferent platform releases can include one or more of the following features. Features useresources in the static region of the platform.Chapter 5: Alveo Platforms lists the features supported by each platform.Table 5: Feature TypesFeatureDescriptionPCIe P2PShorthand forpeer-to-peer communication. Enables direct DMA transfer of data between twoAlveo cards via the PCIe bus without temporarily buffering data within the host DDR memory.Without this feature the host CPU and memory are used for card-to-card communication. For moreinformation, see XRT documentation on PCIe Peer-to-Peer (P2P).M2MEnabling on-card data transfers between card memory resources. Platforms that do not support thisfeature only transfer memory through host CPU and memory. For more information, see XRTdocumentation on Memory-to-Memory (M2M) support.HMShorthand for PCIe host memory transfers. The AXI subordinate interface allows the card FPGA todirectly read and write to host memory, bypassing the DMA. For more information, see XRTdocumentation on PCIe host memory.DFXDynamic function eXchange (DFX) technology allows the card to change functionality on the flywithout power-cycling the server, which enables some platforms to reconfigure DMA links.Current platforms come in one of two DFX variants. DFX-1RP: The PCIe core and the DMA engine are combined and reside in the static region of theplatform. These are also known as one stage platforms.DFX-2RP: The PCIe core resides in the static region of the FPGA (also known as the base) while theDMA engine is dynamically loaded into a new reconfiguration region used by the shell partition.These are also known as two stage platforms.For more information, see Dynamic Function Exchange in XRT Documentation.GTShorthand for Gigabit Transceiver (GT) kernel connection. This platform allows for transceiverconnection of user-provided MAC within an RTL-kernel for in-line QSFP networking access.UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com12

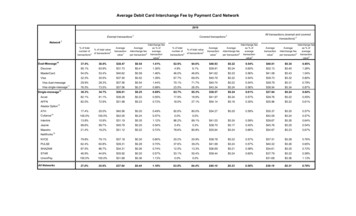

Chapter 5: Alveo PlatformsChapter 5Alveo PlatformsThis section outlines the accelerator cards for data centers and the available target platforms. Atarget platform provides the firmware for the accelerator card running in a specific configuration.A target platform must be installed with Xilinx Runtime (XRT).There can be more than one target platform for a given card. Each platform indicates thecustomization, release name, available features, and tool support. The following sections containspecific details on each available platform. The following table lists the available target platformsper Alveo data center card.RECOMMENDED: Only the following target platforms are supported. Any device or platform that is notlisted is not supported. Xilinx recommends using the latest platform release.Table 6: Available Alveo PlatformsCardRelease NameFeaturesTool SupportP2PM2MHMDFXGT2020.12020.22021.1U50 Gen3x4 XDMA base 2Platform–––1RPYesYesYesYesU50 Gen3x16 XDMA201920 3 Platform–––1RPYesYesYesYesU50LVU50LV Gen3x4 XDMAbase 2 Platform–––1RPYesYesYesYesU200U200 XDMA 201830 2PlatformYesYes–1RP–YesYesYesU250 Gen3x16 XDMA 3 1PlatformYesYesYes2RPYesYesYesU250 Gen3x16 XDMA 2 1PlatformYesYesYes2RPYesU250 XDMA 201830 2PlatformYes––1RP–YesYesYesU280 XDMA 201920 eo PCIe InformationTo view PCIe information for Alveo U200, U250, U280, and U50 cards, see Appendix A in theAlveo Card Out-of-Band Management Specification for Server BMC documentation.UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com13

Chapter 5: Alveo PlatformsU50 and U50LVThe following platforms and the voltages they support are listed in this section. U50 supports VNORM where VCCINT 0.85V U50LV supports VLOW where VCCINT 0.72VThe complete technical specifications are available in the Alveo U50 Data Center Accelerator CardsData Sheet (DS965).UG1120 (v1.4) April 26, 2021Alveo PlatformsSend Feedbackwww.xilinx.com14

Chapter 5: Alveo PlatformsU50 Gen3x16 XDMA 201920 3 Platform Platform name: xilinx u50 gen3x16 xdma 201920 3 Supported by: Vitis tools 2019.2 through 2020.2 Timestamp: 0xf465b0a3ae8c64f6 Release Date: February 2020 Created by: 2019.2 tools Supported XRT versions: 2019.2 PU2 through 2020.2, with support planned through 2021 Satellite controller (SC) FW release: 5.0.27 updated to 5.1.7 with the November 2020 release Link speed: Gen3 x16 Target card: A-U50-P00G-PQ-GFor more information, see Alveo U50 Data Center Accelerator Card. Release Notes: Change log and known issues for the platform and the SC and CMC firmwareare available in the Alveo U50 Master Release Notes Answer Record 75163.The platform implements the device floorplan shown in the following figure and uses resourcesacross the multiple super logic regions (SLR) of the device. The static and dynamic regions areshow

DDR4 channels U200/U250: 4x DDR4 16 GB (64 GB maximum) U280: 2x DDR4 16 GB. Chapter 2: DMA Configurations UG1120 (v1.4) April 26, 2021 www.xilinx.com Alveo Platforms