Transcription

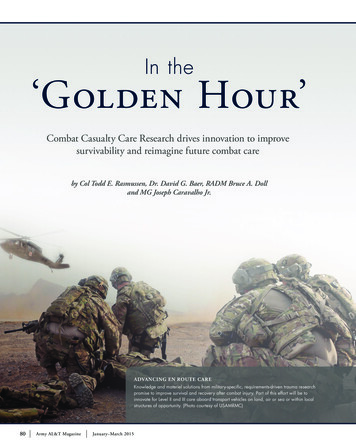

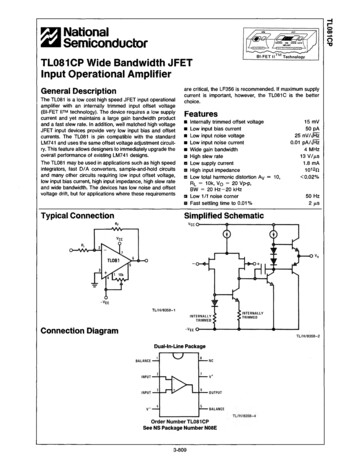

TL081CP5 g NationalJtS i SemiconductorTL081CP Wide Bandwidth JFETInput Operational AmplifierGeneral DescriptionThe TL081 is a low cost high speed JFET input operationalamplifier with an internally trimmed input offset voltage(BI-FET t m technology). The device requires a low supplycurrent and yet maintains a large gain bandwidth productand a fast slew rate. In addition, well matched high voltageJFET input devices provide very low input bias and offsetcurrents. The TL081 is pin compatible with the standardLM741 and uses the same offset voltage adjustment circuit ry. This feature allows designers to immediately upgrade theoverall performance of existing LM741 designs.The TL081 may be used in applications such as high speedintegrators, fast D /A converters, sample-and-hold circuitsand many other circuits requiring low input offset voltage,low input bias current, high input impedance, high slew rateand wide bandwidth. The devices has low noise and offsetvoltage drift, but for applications where these requirementsTypical Connectionare critical, the LF356 is recommended. If maximum supplycurrent is important, however, the TL081C is the betterchoice.Features Internally trimmed offset voltageb Low input bias currentb Low input noise voltagefl Low input noise currentb Wide gain bandwidthm High slew rateB Low supply currentm High input impedancem Low total harmonic distortion Av 10,R l 10k, V0 20 Vp-p,BW 20 Hz- 2 0 kHzm Low 1/ f noise cornerm Fast settling time to 0.01 %Simplified SchematicRfTL/H/8358-1Connection DiagramDual-ln-Line PackageSee NS Package Number N08E3-80915 mV50 pA25 nV/VRz0.01 pAA/Hz4 MHz13 V/jas1.8 mA1012ft 0.02%50 Hz2 JLLS

TL081CPAbsolute Maximum RatingsIf Military/Aerospace specified devices are required,please contact the National Semiconductor SalesOffice/Distributors for availability and specifications.Input Voltage Range (Note 2)Output Short Circuit DurationSupply VoltagePower Dissipation (Notes 1 and 6)Lead Temp. (Soldering, 10 seconds)Operating Temperature RangeS to ra g e 18V670 mWTemperature RangeDC Electrical CharacteristicsSymbol(Note 3)ParameterTL081CConditionsRs 1 0 k a ,T A 25 COver TemperatureAV0S/A TAverage TC of Input OffsetVoltageRs osInput Offset CurrentTj Tj 251004502008Tj Tj 25 C, (Notes 3, 4)70 C 25 CTjLarge Signal Voltage GainVs 15V, T a 25 CV0 1 0 V , R l 2 k HOver TemperatureVoOutput Voltage SwingVs 15V, RLV CMInput Common-Mode VoltageRangeVs CMRRCommon-Mode Rejection RatioRs 1 0 kaPSRRSupply Voltage Rejection Ratio(Note 5) sSupply Current 10 k a25enEquivalent Input Noise VoltageVVV70100dB70100 dB2.8mA(Note 3)TL081CConditionsTypUnitsMaxVs 15V, T a 25 C13V /jllSVs 15V, T a 25 C4MHz25nV/i/Hz0.01pA/Vhlzta 25 c,rs 100 a ,f 1000 HzEquivalent Input Noise CurrentV /m V15-1 2MinGain Bandwidth ProductV /m V1.8ParameterSlew Ratea100 13.5 1115V101215 1 2mVmVtx v rc25 C, (Notes 3,4)70 CInput ResistanceGBW152010r inSR510 k aa volAC Electrical CharacteristicsMax Q. CInput Bias Current UnitsTyp Q. CInput Offset Voltage n150 C260 C120 C/WESD rating to be determined.MinSymbol 115 C 30VDifferential Input Voltage b—65 C to# .A0 C to 7 0 ”CT j(MAX)v OS 15VContinuousTj 25 C, f 1000 HzNote 1: For operating at elevated temperature, the device must be derated based on a thermal resistance of 120 C/W junction to ambient for N package.Note 2: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.Note 3: These specifications apply for Vs 15V and 0 C T a 70 C. Vos. b and los are measured at Vqm 0.Note 4: The input bias currents are junction leakage currents which approximately double for every 10 C increase in the junction temperature, Tj. Due to the limitedproduction test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambienttemperature as a result of internal power dissipation, PD. Tj Ta 0jA pD where 0ja is the thermal resistance from junction to ambient. Use of a heat sink isrecommended if input bias current is to be kept to a minimum.Note 5: Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice fromVs 5V to 15V.Note 6: Max. Power Dissipation is defined by the package characteristics. Operating the part near the Max. Power Dissipation may cause the part to operateoutside guaranteed limits.3-810

TL081CP3-811

TL081CPTypical Performance Characteristics(Continued)Undistorted Output VoltageOpen Loop FrequencyResponseDistortion vs Frequency120I1----- 1----Vsj * 15Vl- 25 Ci11 s2z 2cs v 28)IP P " "1Ay 18010010 560 40 20o !A v - y jo0II180Ik10k100k10k100kFREQUENCY (Hz)1M1FREQUENCY (Hz)Common-Mode RejectionRatio100IK10k100k1M10M0.0151015SUPPLY VOLTAGE ( V)20i-i i10k 100k 1M 10M101001k10k100kFREQUENCY (Hz)Inverter Settling TimeOutput Impedanceio oIkEquivalent Input NoiseVoltageFREQUENCY (Hz)Open Loop Voltage Gain (V/V)100FREQUENCY (Hz)Power Supply Rejection1010 ---- ---- ---- ---- ---100Ik10k100kFREQUENCY (Hz)1M10Mo .ii SETTLING TIME (ps)TL/H /8358-63-812

TL081CPPulse ResponseSmall Signal Non-InvertingSmall Signal InvertingTIME (0.2 jus/DIV)TIME (0.2 ps/DIV)TL/H/8358-13TL/H/8358-7Large Signal Non-InvertingLarge Signal InvertingTIME (2 ps/DIV)TIME (2 /is/DIV)TL/H/8358-14TL/H/8358-15Current Limit (Rl 100fi)TIME (5 ms/DIV)TL/H/8358-16Application Hintswill cause large currents to flow which can result in a de stroyed unit.The TL081 is an op amp with an internally trimmed inputoffset voltage and JFET input devices (BI-FET II). TheseJFETs have large reverse breakdown voltages from gate tosource and drain eliminating the need for clamps across theinputs. Therefore, large differential input voltages can easilybe accommodated without a large increase in input current.The maximum differential input voltage is independent ofthe supply voltages. However, neither of the input voltagesshould be allowed to exceed the negative supply as thisExceeding the negative common-mode limit on either inputwill force the output to a high state, potentially causing areversal of phase to the output.Exceeding the negative common-mode limit on both inputswill force the amplifier output to a high state. In neither casedoes a latch occur since raising the input back within the3-813

TL081CPApplication Hints (Continued)common-mode range again puts the input stage and thusthe amplifier in a normal operating mode.resulting forward diode within the IC could cause fusing ofthe internal conductors and result in a destroyed unit.Exceeding the positive common-mode limit on a single inputwill not change the phase of the output; however, if bothinputs exceed the limit, the output of the amplifier will beforced to a high state.Because these amplifiers are JFET rather than MOSFETinput op amps they do not require special handling.As with most amplifiers, care should be taken with leaddress, component placement and supply decoupling in or der to ensure stability. For example, resistors from the out put to an input should be placed with the body close to theinput to minimize “ pick-up” and maximize the frequency ofthe feedback pole by minimizing the capacitance from theinput to ground.The amplifier will operate with a common-mode input volt age equal to the positive supply; however, the gain band width and slew rate may be decreased in this condition.When the negative common-mode voltage swings to within3V of the negative supply, an increase in input offset voltagemay occur.A feedback pole is created when the feedback around anyamplifier is resistive. The parallel resistance and capaci tance from the input of the device (usually the inverting in put) to AC ground set the frequency of the pole. In manyinstances the frequency of this pole is much greater thanthe expected 3 dB frequency of the closed loop gain andconsequently there is negligible effect on stability margin.However, if the feedback pole is less than approximately 6times the expected 3 dB frequency a lead capacitor shouldbe placed from the output to the input of the op amp. Thevalue of the added capacitor should be such that the RCtime constant of this capacitor and the resistance it parallelsis greater than or equal to the original feedback pole timeconstant.The TL081 is biased by a zener reference which allows nor mal circuit operation on 4V power supplies. Supply volt ages less than these may result in lower gain bandwidth andslew rate.The TL081 will drive a 2 k n load resistance to 10V overthe full temperature range of 0 C to 70 C. If the amplifieris forced to drive heavier load currents, however, an in crease in input offset voltage may occur on the negativevoltage swing and finally reach an active current limit onboth positive and negative swings.Precautions should be taken to ensure that the power sup ply for the integrated circuit never becomes reversed in po larity or that the unit is not inadvertently installed backwardsin a socket as an unlimited current surge through theDetailed SchematicHI- - 03TL/H /8358-83-814

TL081CPTypical ApplicationsHi-ZiN Inverting AmplifierSupply Current Indicator/LimiterC2 Vqut switches high when RsIs VqParasitic input capacitance C1 (3 pF for TL081 plus any additionallayout capacitance) interacts with feedback elements and creates un desirable high frequency pole. To compensate, add C2 such that:R2C2 R1C1.Ultra-Low (or High) Duty Cycle PulseGeneratorLong Time Integrator4.8 - 2VS OUTPUT HIGH R1C / n TL/H /8358-12* Low leakage capacitor* toUTPUT LOW R2C / n7 50k pot used for less sensitive Vqs adjustwhere Vs V v- *low leakage capacitor3-815

currents. The TL081 is pin compatible with the standard LM741 and uses the same offset voltage adjustment circuit ry. This feature allows designers to immediately upgrade the overall performance of existing LM741 designs. The TL081 may be used in applications such as high speed integrators, fast D/A converters, sample-and-hold circuits