![The Design Of A Comparator [The Analog Mind]](/img/21/br-sscm-4-2020.jpg)

Transcription

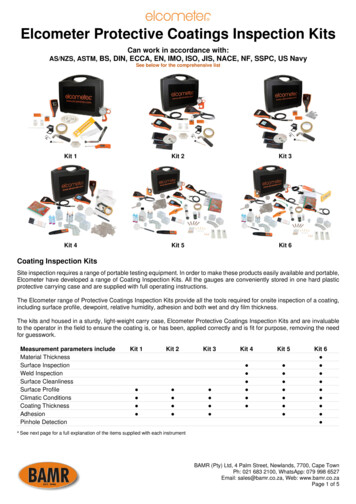

TH E ANALOG M IN DBehzad RazaviThe Design of a ComparatorNNyquist-rate and oversampling analog-to-digital converters (ADCs) incorporate comparators to performquantization and possibly sampling.Comparators thus have a significantimpact on the speed and precisionof ADCs. This article presents thestep-by-step design of a comparator and the discovery of its varioustrade-offs.General ConsiderationsA comparator senses a differentialinput and generates a logical outputaccording to the polarity of the inputdifference. In an ADC environment,we are interested in the followingcomparator design parameters: input offset, speed, power consumption, metastability, kickback noise,and input-referred electronic noise.The design begins with the selectionof target values for some of these parameters. Here, we aim for an inputoffset lower than 5 mV; a clock rate,fCK, of 5 GHz; and a power consumption of 1 mW. After the design meetsthese requirements, we examine theremaining parameters and decidewhether they are adequate.For this article, we selected theStrongArm latch as the comparatorcore. Readers are referred to [1]–[4]for the properties and operation details of the circuit. Shown in Figure1, this topology offers several desirable attributes: it requires a singleclock phase; draws no static power;exhibits an input offset that arisesprimarily from the input pair, M1and M2; and delivers rail-to-rail output swings [4].A brief overview of the StrongArm latch’s operation proves helpfulhere. As explained in [4], the circuitof Figure 1 begins by prechargingnodes P, Q, X, and Y to VDD. We denotethe capacitances at these nodes byC P , C Q , C X , and CY, respectively, andassume that C P C Q and C X C Y .When CK goes high, M1 and M2 actas a differential pair with capacitiveloads, and VP and VQ fall from VDDwhile yielding a differential component proportional to Vin1 - Vin2 . Thismode continues until VP and VQ dropto roughly VDD - VTH3,4, creating avoltage gain approximately equal to2g m1, 2 VTH3,4 /I SS, where g m1, 2 denotesthe transconductance of M1 and M2,and I SS is the tail current [3]. At theend of this mode, M3 and M4 turnon, causing VX and V Y to fall until M5and M 6 are activated. One output isthen pulled back to VDD by M5 or M 6while the other falls to zero. As examined in [4], the role of M3 and M4is to cut the current path from VDD tothe ground after the comparator hasmade a decision. The circuit’s powerconsumption in the signal path is2given by 2fCK C P V 2DD fCK C X V DD[4].Additionally, the clock path draws apower of fCK C CK V 2DD, where CCK is thesum of the gate capacitances of M7and the four PMOS switches, S1–S 4.T he precha rge act ion in t heStrongArm latch offers two benefits.First, it enables VP and VQ in Figure 1to begin from VDD, thus keeping M1and M2 in saturation for some time.This allows the input transistorsto provide gain. Second, after eachcomparison, the four internal nodesrecover from the states developedon them and are “equalized.” Thisensures that the states in one clockcycle are not inherited by the next,suppressing “dynamic” offsets. Asdepicted in Figure 2, if, at the endof the precharge mode, VP and VQ donot become exactly equal and bear adifference of DV, the subsequent amplification mode begins with such adifference stored on CP and CQ , suffering from 68FA L L 2 0 2 0M7FIGURE 1: The StrongArm latch and its waveforms.IEEE SOLID-STATE CIRCUITS MAGAZINEVYVQVXVin2Digital Object Identifier 10.1109/MSSC.2020.3021865Date of current version: 18 November 2020VPVDDM4PCKCKM6t1t

Most of our design effort is expended on selecting the transistordimensions in Figure 1. We generallybegin with near-minimum dimensions unless there is a compellingreason not to do so. Also, our simulations are performed under worstcase process, supply voltage, andtemperature (PVT) conditions becausethe circuit must eventually operate satisfactorily in such a corner. Inthis spirit, we select the slow-slowcorner, VDD 1 V - 5% 0.95 V, andT 75c C. We also assume for theclock a 50% duty cycle and 10-ps riseand fall times. The comparator is designed using 28-nm CMOS technology.Choice of Device DimensionsComparator design begins with selecting the transistor dimensions soas to meet the offset requirement.In our case, the pairs M1 and M2, M3and M4, and M5 and M 6 in Figure 1 appear in the signal path and must becrafted first. Let us consider M1 andM2 and write their threshold voltagemismatch asDVTH1,2 A VTH , (1)(WL) 1, 2where AVTH is a constant [5] androughly 2.2 mV µm in 28-nm technology. If we choose W 1, 2 10 nmand an effective length of 25 nm,then DVTH 4.4 mV. This appears tobe a reasonable starting point provided that the other pairs’ contributions do not raise the offset beyondthe 5-mV target.We should remark that (1) givesthe standard deviation, v, of themismatch; i.e., approximately 68%of the differential pairs in a Gaussian distribution exhibit offsets lessthan this amount. In practice, weseek higher yields and must eitherenlarge the transistors or incorporate offset cancellation.The tail transistor M7 in Figure 1must draw sufficient current withVGS7 VDD and VDS7 Vin, CM - VGS1,2,where Vin, CM denotes t he inputcom mon -mo de (CM ) level. Wit hVin, CM 0.5 V and VGS1, 2 . 0.35 V, wehave VDS7 . 0.15 V. The device thusoperates in the deep triode region.Let us select W 7 2 nm for a currentof roughly 0.5 mA.Given that the circuit provides gainbefore M3 and M4 turn on, we expectthat the offset of this pair is reducedwhen referred to the main input. Thereduction factor is, in fact, greaterthan the value of 2g m1, 2 VTH3,4 /I SSmentioned previously. To understand why, suppose M3 and M4 are on(Figure 3) and neglect the capacitances at nodes P and Q. Thus, I D1 andI D2 entirely flow through M3 and M4,respectively, as if these transistorswere absent. The offset contributedby this pair is therefore negligibleunless the circuit’s capacitances aretaken into account. As discussed later in this section, the threshold mismatch between M3 and M4 is dividedby a factor of 3–5 in typical designs.We select W 3, 4 10 nm for now, expecting that this choice only slightlyraises the input offset.The PMOS cross-coupled pair inFigure 1 turns on after VX and V Yfall by one 1-PMOS threshold. Beforethis time, the circuit provides a highvoltage gain, thereby reducing thispair’s offset contribution considerably. In this respect, we surmisethat a width of a few microns suffices for M5 and M 6, but we mustbear in mind that these devices alsoamplify regeneratively and play arole in the comparator’s speed. Wereturn to this point when we optimize the design.The reset switches S1–S 4 in Figure 1 must pull their drain nodes toVDD in under 100 ps. We predict thata width of 0.5–1 μm can meet thisconstraint.Basic WaveformsBased on our foregoing thoughts, weconstruct the comparator shown inFigure 4 and simulate it in the timedomain. The output inverters act asbuffers and employ relatively smalltransistors for now. Before optimizing the design, we familiarize ourselves with the circuit’s waveforms.VDD VVPVQTCKtComparison PrechargeFIGURE 2: An example of dynamic offset.ID1 IXID2XYM3M4PQM1Vin1CKM2Vin2M7FIGURE 3: The effect of the mismatchbetween M3 and M4 in the absence of capacitances at P and Q.VDDCKS1S3M5M6VoutXQM1CKS2M4PVin1S4YM3M2WP 400 nmCKVin2M7XWN 200 nmS1–S4: W 0.5 µmWP 400 nmW5,6 2.5 µmW3,4 10 µmYW1,2 10 µmWN 200 nmW7 2 µmL 28 nmFIGURE 4: The initial design of the comparator core.IEEE SOLID-STATE CIRCUITS MAGAZINEFA L L 2 0 2 09

1800Current (µA)Voltage (V)0.80.6VYVXVPVQ0.40.260040020000300350400Time (ps)450500300(a)350400Time (ps)450500(b)FIGURE 5: The comparator’s (a) voltage waveforms and (b) tail current waveform.The speed of the comparatordepends on the input voltage difference, ultimately requir ing ametastability analysis (as explainedlater). However, it is common in ADCdesign to select this difference tobe half of the least-significant bit,which, in view of our tolerable offset, would be 10–20 mV for this design. However, we apply a differenceof 1 mV so as to place the circuit in“slow motion” and examine its operation details. Plotted in Figure 5(a)are the voltages at nodes P, Q, X,and Y. The clock rises from zero toVDD between t 300 and t 310 ps.Note that VX and V Y experience a CMdrop of approximately 400 mV be-fore they begin to depart as a resultof the regeneration provided by M5and M 6. We also observe from Figure 5(b) that the tail current reachesa peak of roughly 800 μA before VPand VQ drop enough to drive theinput transistors into the triode region and cause the tail node voltageto collapse.F i g u r e 6 p l o t s VP - VQ f o rVin1 - Vin2 1mV. Two observationsprove important here. First, as shownin the inset, VP - VQ reaches 3.15 mVat t 315 ps, the greatest differencebefore M3 and M4 turn on. That is, theinitial voltage gain is equal to 3.15.Second, VP - VQ is less than 100 μV att 500 ps, i.e., before the next clock0–1–2–3–40.1Voltage (V)0.05305 310 315 320 3250–0.05–0.1300350400450Time (ps)FIGURE 6: The difference between VP and VQ as a function of time.10FA L L 2 0 2 0IEEE SOLID-STATE CIRCUITS MAGAZINE500cycle. Thus, the precharge devicesare strong enough, and the dynamicoffset is negligible.For design optimization, we needa metric for the circuit’s speed. Forexample, we can find the time ittakes for VX - VY to reach a certainamount, say, 200 mV. This time ismeasured with respect to when theclock’s rising edge crosses VDD /2,and is equal to 36 ps in Figure 5(a).Offset and Speed OptimizationFor the design in Figure 4, we mustquantify the input offset contributed by both the M3 and M4 pairand the M5 and M 6 pair. To this end,we place a voltage source equal toDVTH3,4 4.4 mV in series with thegate of M 3 while the other pairsremain matched [Figure 7(a)]. Wethen adjust the input voltage difference so that the circuit is nearlybalanced and VX - VY tends to staynear zero for a relatively long time.With some iteration, we find thatVin1 - Vin2 . 1.15 mV leads to such abehavior [see Figure 7(b)]. This suggests that the offset of M3 and M4 isdivided by a factor of 4.4/1.15 3.8when referred to the input. Theoffset standard deviation arisingfrom both the M1 and M2 pair andthe M3 and M4 pair is thus given by(4.4 mV) 2 (1.15 mV) 2 4.5 mV.Given the small offset contribution of M3 and M4, we ask whether theirwidths can be reduced so as to increasethe speed. Indeed, if W 3, 4 5 nm, then

XM3– VTHPVin1YM4 M1QM20.8VYVX0.60.40.2M7CK0300(a)350400Time (ps)(b)450500FIGURE 7: (a) The inclusion of the mismatch between M3 and M4 and (b) the output waveforms when the circuit is nearly balanced.10.8VYVYVXVX0.60.40.20300320340Time (ps)360380FIGURE 8: The comparator output waveforms for W7 2 μm and 4 μm, respectively.VDDAddition of the Reset-Set LatchIn the precharge mode, the StrongArm comparator’s decision is erased,and the outputs do not represent avalid logical level, potentially confusing the following stages. To resolve this issue, we insert a reset-set(RS) latch in the output path. As illustrated in Figure 9, the RS latchcan change its state only if M11 orM12 turns on, i.e., when VX or V Y fallsto zero. This latch then retains thestate as the StrongArm circuit enters the precharge mode.Vin2Voltage (V)1Voltage (V) VX - VY reaches 200 mV in 28 ps. Atest similar to that in Figure 7(a) withDVTH3,4 A VTH / WL 6.2 mV indicates an input contribution of 1.5 mV.That is, the offset rises from 4.5 mVto (4.4 mV) 2 (1.5 mV) 2 4.6 mV.The small increase in the offset makesW 3, 4 5 nm a more favorable choice.In the next step of optimization,we turn to M5 and M6 in Figure 4 andquantify their offset contribution. With W 5, 6 2.5 nm, we haveDVTH5,6 8.8 mV. Inserting this voltage in series with the gate of M5 or M6and repeating the procedure of Figure7(a), we arrive at an input contributionequal to 0.9 mV. The total input offset is(4.4 mV) 2 (1.5 mV) 2 (0.9 mV) 2 4.7 mV. If we double the widths ofM5 and M6, their input contributionis still roughly 0.9 mV because theirlarger capacitances lower the voltagegain developed by the circuit beforethis pair turns on. We therefore retain W 5, 6 2.5 nm. The offset calculations can be verified throughthe use of Monte Carlo simulationsthat incorporate the foundry’s mismatch models.It is possible to increase the comparator’s speed by raising the tail current, i.e., by widening M7 in Figure 4.Plotted in Figure 8 are VX and VY forW 7 2 and 4 μm, respectively. Thetime necessary for VX - VY to reach200 mV drops from 28 to 22 ps. Interestingly, the power consumed in the2signal path, 2fCK C P V 2DD fCK C X V DD,remains fairly constant, but the clockpath draws greater power. As explained later, a wider M7 translates tohigher kickback noise.WP 400 nmXM13M14ABM11WN 200 nmM12W13,14 400 nmW11,12 400 nmWP 400 nmYL 28 nmWN 200 nmFIGURE 9: An RS latch following the comparator.IEEE SOLID-STATE CIRCUITS MAGAZINEFA L L 2 0 2 011

VBVBVAVA0.80.6Voltage (V)clock period, we say the circuit is“metastable” [Figure 11(a)]. Duringmetastability, the indefinite nature of the comparator outputs canpropagate to the subsequent logic,introducing large errors. This issuebecomes particularly serious in digital communication systems wherethe error rate must be extremelylow, e.g., 10 -14 .In the StrongArm latch of Figure 4, M5 and M 6 serve as the primary amplifying circuit during ametastable state. From the modelshown in Figure 11(b), we can provethat the positive feedback aroundthe loop is characterized by0.40.20110120130140150Time (ps)VXY VXY0 exp t , (2)x regFIGURE 10: The RS latch outputs for the original and modified designs.VDDVDDVXY0M5VYVXCXTCKM6XYCYt2(a)(b)VXY0 V1 expFIGURE 11: (a) Comparator metastability and (b) the behavior of PMOS transistors duringthis period.The RS latch’s delay proves critical in some ADC architectures andmust be minimized. Since the latchoperates by pulling one output low,we surmise that M11 and M12 mustbe relatively wide. Moreover, if weincrease the width of the inverters’ PMOS devices, their outputsrise with less delay. We then changeW 11, 12 to 800 nm and also the inverters’ PMOS widths to 800 nm. Asshown in Figure 10, the total delaynow drops by 6 ps. The overall comparator circuit draws approximately0.2 mW at 5 GHz.to-peak swing of 2A 0 with a uniformdistribution, then the probabilitythat the difference (positive or negative) presented to the comparator isless than DV is equal to DV/A 0 .Upon sensing a small difference,a comparator takes some time togenerate a well-defined logical output. If it cannot do so in half of the V VαMetastabilityIn an ADC environment, a comparator senses a random signal at themoment it is clocked. Thus, its inputdifference can be arbitrarily small.For example, if the signal has a peak-12FA L L 2 0 2 0VYwhere VXY0 denotes the initial value,and the regeneration time constant,x reg, is given by g m5, 6 /C X . Note thatthis expression is valid only after theinitial fall of VX and V Y . If VXY is notlarge enough after TCK /2 seconds towrite a well-defined state onto theRS latch, an error can occur. Denoting the minimum acceptable valueof VXY by V1, we require thatτreg In αVXInput differences that yield a VXY0 lessthan this value cause a metastabilityerror. The error rate is therefore proportional to exp [- TCK / (2x reg)], underscoring the high impact of x reg .We can compute x reg by measuring g m5, 6 and CX in Figure 4. Alternatively, we can obtain x reg directlyfrom simulations. Consider the tworegeneration scenarios depicted inFigure 12, where VXY0 is chosen equalto some amount, DV, or a smalleramount, DV/a. We denote VX - VYfor the two cases by VXY1 and VXY2, respectively, and write from (2)VXY 2 DV exp t (4)ax reg DV exp (- ln a) exp t (5)x reg DV exptFIGURE 12: A shift of regeneration response for different initial conditions.IEEE SOLID-STATE CIRCUITS MAGAZINE- TCK /2. (3)x regt - x reg ln a. (6)x regInterestingly, VXY2 is simply equalto VXY1 but shifted by x reg ln a. Forthe design in Figure 4, we select an

input difference of 1 mV, 100 μV, and10 μV, thus arriving at the waveformsshown in Figure 13. The time shift ineach case is 5.7 ps and implies thatx reg 5.7 ps/ ln 10 2.5 ps.Can we reduce x reg by adjusting t he w idt hs of M 5 a nd M 6 inFig ur e 4? If W 5, 6 is doubled, thesetwo devices’ capacitances double,but their transconductance rises byroughly a factor of 2 . That is, x regdecreases only if M5 and M 6 do notdominate the capacitance at X andY. In our design, changing W 5, 6 from2.5 to 5 μm increases x reg slightly.The foregoing observations prescribea simple method for estimating the input difference VXY0 in (3), which leads toan error. We first simulate the comparator with a moderate value for Vin1 - Vin2,e.g., 1 mV, and find the delay, e.g., 22 ps.We also recognize that 1) reducingVin1 - Vin2 by a factor of 10 n shifts theresponse by nx reg ln 10 and 2) if theshift exceeds TCK /2 - 22 ps, an error islikely to occur. In our design,nx reg ln 10 .0.8Voltage (V)VXVY0.6VXVY0.4VXVY0.20300320340Time (ps)FIGURE 13: The output waveforms of the comparator for input differences equal to 1 mV,100 μV, and 10 μV.This means that the capacitances seenat the inverters’ inputs are also slightly unequal (due to the Miller effect oftheir gate-drain parasitics). This deterministic imbalance causes the StrongArm latch to favor one logical outputfor very small input differences. Wetherefore disconnect the RS latch forsuch simulations. Alternatively, we canshort A and B to VDD so as to maintainthe loading presented to the inverters.Another metastability simulationissue relates to the simulator’s accuracies. In Cadence, we set threeparameter as follows: reltol 10 -6,vabstol 10 -6, and iabstol 10 -12 .TCK- 22ps , (7)2. 78 ps (8)and, hence, n . 13.5. It follows thatinput differences of 1 mV/10 13.5may generate errors.We should remark that simulating acomparator with very small input differences, e.g., 1 fV, requires minimizing all the sources of asymmetry in thecircuit and in the simulation tool. Specifically, the presence of the RS latch inFigure 9 does lead to a slight asymmetry in the StrongArm circuit. Supposethe stored state is VA 0 and VB VDD.As a result, the gate input capacitancesof M11 and M12 are slightly different.comparator’s time-domain decisionis randomly affected by the noise ofits constituent devices. We first setVin1 - Vin2 to zero [Figure 14(a)] andensure that the logical output assumesa value of zero or one with equal probabilities. Plotted in Figure 15(a) areVX and VY, in this case, for 100 clockcycles. We observe that VX goes to zeroapproximately 50 times.Next, we select a small, constantvalue for Vin1 - Vin2 so as to skew thedecisions [see Figure 14(b)]. We recallthat the area under a Gaussian distribution from - v to v is equal to68% and hence that from - 3 to - vis 100% - (34% 50%) 16%. Thus, ifVS is chosen so as to reduce the probability of zeros to 16%, then VS v,which is also the total root-meansquare (rms) noise referred to the input. After a few iterations, we observethe waveforms in Figure 15(b), whereVX goes to zero roughly 16 times forInput-Referred NoiseThe standard method of computingthe output noise and dividing it by thegain does not apply to comparatorsbecause they produce a digital output. As explained in [4], we perform atransient noise simulation so that thefX(x )fX(x )Probability ofOnesProbability ofZerosVoutCK(a)3600VS –VoutCKx(b)Probability ofZerosProbability ofOnes–VS 0xFIGURE 14: (a) A perfectly balanced comparator generates ones and zeros with equal probabilities; (b) a finite input imbalanceskews the decisions.IEEE SOLID-STATE CIRCUITS MAGAZINEFA L L 2 0 2 013

1.2VYVXVoltage (V)10.80.60.40.20–0.20246810Time (ns)(b)12141618201.2VYVXVoltage (V)10.80.60.40.20–0.20246810Time (ns)(a)1214161820FIGURE 15: The comparator outputs (a) for perfect balance and (b) with an input difference equal to 0.31 mV.200Iin1Iin2150Current (µA)100500–50and the latter prove problematic generally. Kickback noise trades with thedimensions of the input transistorsand hence with the offset voltage. Butthe timing of this noise determineswhether it has an adverse effect on theperformance. For example, we expectthe noise around t 300 ps in Figure 16 to be more serious, as it coincideswith the comparator’s decision time.–100References–150–200300350400Time (ps)450FIGURE 16: The input kickback noise currents of a StrongArm comparator.VS 0.31mV. The comparator’s input rms noise is approximately equalto this value. For greater precision,we can run the two simulations for alarger number of clock cycles.Kickback NoiseThe StrongArm latch draws large transient currents from its inputs duringswitching. Called the kickback noise,this phenomenon proves undesirableif it affects the comparator’s own deci-14FA L L 2 0 2 0sion or corrupts the input voltage whileit is sensed by other circuits. For example, in a flash ADC, all of the comparators generate kickback noise while onemust make a critical decision. Figure 16plots the kickback noise currents ofour design when Vin1 - Vin2 1mV.The clock begins to rise at t 300 ps.We recognize that the two exhibit bothCM and differential components. Theformer are objectionable if they flowthrough unequal source impedances,IEEE SOLID-STATE CIRCUITS MAGAZINE[1] J. Montanaro et al., “A 160-MHz 32-b0.5-W CMOS RISC microprocessor,” IEEEJ. Solid-State Circuits, vol. 31, no. 11,pp. 1703–1714, Nov. 1996. doi: 10.1109/JSSC.1996.542315.[2] T. Kobayashi, K. Nogami, T. Shirotori, Y.Fujimoto, and O. Watanabe, “A currentmode latch sense amplifier and a staticpower saving input buffer for low-powerarchitecture,” in Proc. VLSI Circuits Symp.Dig. Tech. Papers, June 1992, pp. 28–29.doi: 10.1109/VLSIC.1992.229252.[3] P. Nuzzo, F. De Bernardinis, P. Terreni,and G. Van der Plas, “Noise analysis ofregenerative comparators for reconfigurable ADC architectures,” IEEE Trans.Circuits Syst. I, Reg. Papers, vol. 55, no. 6,pp. 1441–1454, July 2008. doi: 10.1109/TCSI.2008.917991.[4] B. Razavi, “The StrongARM Latch [a circuitfor all seasons],” IEEE Solid State CircuitsMag., vol. 7, no. 2, pp. 12–17, Spring 2015.doi: 10.1109/MSSC.2015.2418155.[5] M. J. M. Pelgrom, A. C. J. Duinmaijer, andA. P. G. Welbers, “Matching properties ofMOS transistors,” IEEE J. Solid-State Circuits, vol. 24, no. 5, pp. 1433–1440, Oct.1989. doi: 10.1109/JSSC.1989.572629.

THE ANALOG MIND Behzad Razavi N Nyquist-rate and oversampling ana-log-to-digital converters (ADCs) in-corporate comparators to perform quantization and possibly sampling. Comparators thus have a significant impact on the speed and precision of ADCs. This article presents the step-by-step design