Transcription

AMBA 3 AHB-Lite Protocol v1.0SpecificationCopyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

AMBA 3 AHB-Lite ProtocolSpecificationCopyright 2001, 2006 ARM Limited. All rights reserved.Release InformationChange historyDateIssueConfidentialityChange06 June 2006ANon-ConfidentialFirst release for v1.0Proprietary NoticeWords and logos marked with or are registered trademarks or trademarks of ARM Limited in the EU andother countries, except as otherwise stated below in this proprietary notice. Other brands and namesmentioned herein may be the trademarks of their respective owners.Neither the whole nor any part of the information contained in, or the product described in, this documentmay be adapted or reproduced in any material form except with the prior written permission of the copyrightholder.The product described in this document is subject to continuous developments and improvements. Allparticulars of the product and its use contained in this document are given by ARM in good faith. However,all warranties implied or expressed, including but not limited to implied warranties of merchantability, orfitness for purpose, are excluded.This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liablefor any loss or damage arising from the use of any information in this document, or any error or omission insuch information, or any incorrect use of the product.AMBA Specification License1.Subject to the provisions of Clauses 2 and 3, ARM hereby grants to LICENSEE a perpetual, non-exclusive,nontransferable, royalty free, worldwide licence to use and copy the AMBA Specification for the purpose ofdeveloping, having developed, manufacturing, having manufactured, offering to sell, selling, supplying orotherwise distributing products which comply with the AMBA Specification.2.THE AMBA SPECIFICATION IS PROVIDED “AS IS” WITH NO WARRANTIES EXPRESS, IMPLIEDOR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORYQUALITY, MERCHANTABILITY, NONINFRINGEMENT OR FITNESS FOR A PARTICULARPURPOSE.3. No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, touse the ARM tradename, or AMBA trademark in connection with the AMBA Specification or any productsbased thereon. Nothing in Clause 1 shall be construed as authority for LICENSEE to make anyrepresentations on behalf of ARM in respect of the AMBA Specification.iiCopyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

Confidentiality StatusThis document is Non-Confidential. The right to use, copy and disclose this document may be subject tolicense restrictions in accordance with the terms of the agreement entered into by ARM and the party thatARM delivered this document to.Product StatusThe information in this document is final, that is for a developed product.Web Addresshttp://www.arm.comARM IHI 0033ACopyright 2001, 2006 ARM Limited. All rights reserved.iii

ivCopyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

ContentsAMBA 3 AHB-Lite Protocol SpecificationPrefaceAbout this book . xiiFeedback . xviChapter 1Introduction1.11.21.3Chapter 2Signal Descriptions2.12.22.32.42.5Chapter 3Global signals .Master signals .Slave signals .Decoder signals .Multiplexor signals .2-22-32-52-62-7Transfers3.13.23.33.43.5ARM IHI 0033AAbout the protocol . 1-2Operation . 1-5Multi-layer AHB-Lite . 1-6Basic transfers .Transfer types .Locked transfers .Transfer size .Burst operation .Copyright 2001, 2006 ARM Limited. All rights reserved.3-23-53-73-83-9v

Contents3.63.7Chapter 4Bus Interconnection4.14.2Chapter 5Slave transfer responses . 5-2Data Buses6.16.2Chapter 7Address decoding . 4-2Bus interconnection . 4-3Slave Response Signaling5.1Chapter 6Waited transfers . 3-16Protection control . 3-22Data buses . 6-2Data bus width . 6-5Clock and Reset7.1Clock and reset requirements . 7-2GlossaryviCopyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

List of TablesAMBA 3 AHB-Lite Protocol SpecificationTable 2-1Table 2-2Table 2-3Table 2-4Table 2-5Table 3-1Table 3-2Table 3-3Table 3-4Table 5-1Table 5-2Table 6-1Table 6-2ARM IHI 0033AChange history . iiGlobal signals . 2-2Master signals . 2-3Slave signals . 2-5Decoder signals . 2-6Multiplexor signals . 2-7Transfer type encoding . 3-5Transfer size encoding . 3-8Burst signal encoding . 3-9Protection signal encoding . 3-22HRESP signal . 5-2Transfer response . 5-2Active byte lanes for a 32-bit little-endian data bus . 6-3Active byte lanes for a 32-bit big-endian data bus . 6-3Copyright 2001, 2006 ARM Limited. All rights reserved.vii

List of TablesviiiCopyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

List of FiguresAMBA 3 AHB-Lite Protocol SpecificationFigure 1-1Figure 1-2Figure 1-3Figure 1-4Figure 3-1Figure 3-2Figure 3-3Figure 3-4Figure 3-5Figure 3-6Figure 3-7Figure 3-8Figure 3-9Figure 3-10Figure 3-11Figure 3-12Figure 3-13Figure 3-14Figure 3-15Figure 3-16Figure 3-17Figure 4-1ARM IHI 0033AKey to timing diagram conventions . xivAHB-Lite block diagram . 1-2Master interface . 1-3Slave interface . 1-4Example multi-layer AHB-Lite block diagram . 1-6Read transfer . 3-2Write transfer . 3-2Read transfer with wait states . 3-3Write transfer with wait state . 3-3Multiple transfers . 3-4Transfer type examples . 3-6Locked transfer . 3-7Four-beat wrapping burst . 3-12Four-beat incrementing burst . 3-13Eight-beat wrapping burst . 3-13Eight-beat incrementing burst . 3-14Undefined length bursts . 3-15Waited transfer, IDLE to NONSEQ . 3-16Waited transfer, BUSY to SEQ for a fixed length burst . 3-17Waited transfer, BUSY to NONSEQ for an undefined length burst . 3-18Address changes during a waited transfer, with an IDLE transfer . 3-19Address changes during a waited transfer, after an ERROR . 3-20Slave select signals . 4-2Copyright 2001, 2006 ARM Limited. All rights reserved.ix

List of FiguresFigure 4-2Figure 5-1Figure 6-1Figure 6-2xMultiplexor interconnection .ERROR response .Narrow slave on a wide bus .Wide slave on a narrow bus .Copyright 2001, 2006 ARM Limited. All rights reserved.4-35-46-56-6ARM IHI 0033A

PrefaceThis preface introduces the Advanced Microcontroller Bus Architecture (AMBA) 3AHB-Lite Protocol Specification. It contains the following sections: About this book on page xii Feedback on page xvi.ARM IHI 0033ACopyright 2001, 2006 ARM Limited. All rights reserved.xi

PrefaceAbout this bookThis is the specification for the AMBA 3 AHB-Lite protocol.Intended audienceThis book is written to help hardware and software engineers design systems andmodules that are compliant with the AHB-Lite protocol.Using this specificationThis specification is organized into the following chapters:Chapter 1 IntroductionRead this chapter for an overview of the AHB-Lite protocol.Chapter 2 Signal DescriptionsRead this chapter for descriptions of the signals.Chapter 3 TransfersRead this chapter for information about the different types of transferinitiated by an AHB-Lite compliant master.Chapter 4 Bus InterconnectionRead this chapter for information about the additional interconnect logicrequired for AHB-Lite systems.Chapter 5 Slave Response SignalingRead this chapter for information about the slave response signaling.Chapter 6 Data BusesRead this chapter for information about the read and write data buses andhow to interface to different data bus widths.Chapter 7 Clock and ResetRead this chapter for information about the clock and reset signals.GlossaryRead the Glossary for definitions of terms used in this specification.ConventionsThis section describes the conventions that this specification uses: Typographical on page xiiixiiCopyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

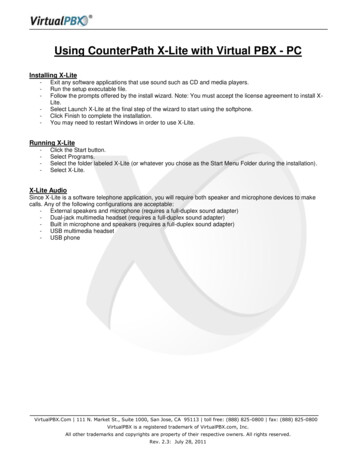

Preface Timing diagramsSignals on page xiv.TypographicalThe typographical conventions are:italicHighlights important notes, introduces special terminology,denotes internal cross-references, and citations.boldHighlights interface elements, such as menu names. Denotessignal names. Also used for terms in descriptive lists, whenappropriate.monospaceDenotes text that you can enter at the keyboard, such ascommands, file and program names, and source code.monospaceDenotes a permitted abbreviation for a command or option. Youcan enter the underlined text instead of the full command or optionname.monospace italicDenotes arguments to monospace text where the argument is to bereplaced by a specific value.monospace boldDenotes language keywords when used outside example code. and Angle brackets enclose replaceable terms for assembler syntaxwhere they appear in code or code fragments. They appear innormal font in running text. For example: MRC p15, 0 Rd , CRn , CRm , Opcode 2 The Opcode 2 value selects which register is accessed.Timing diagramsThe figure named Key to timing diagram conventions on page xiv explains thecomponents used in timing diagrams. Variations, when they occur, have clear labels.You must not assume any timing information that is not explicit in the diagrams.Shaded bus and signal areas are undefined so the bus or signal can assume any valuethat the shaded area represents. The actual level is unimportant and does not affectnormal operation.ARM IHI 0033ACopyright 2001, 2006 ARM Limited. All rights reserved.xiii

Preface&ORFN ,* WR /2:7UDQVLHQW ,* /2: WR ,* %XV VWDEOH%XV WR KLJK LPSHGDQFH%XV FKDQJH LJK LPSHGDQFH WR VWDEOH EXVKey to timing diagram conventionsNoteSingle-bit signals are sometimes shown as HIGH and LOW at the same time and theylook similar to the bus change shown in Key to timing diagram conventions. If asingle-bit signal is shown like this then its value does not affect the accompanyingdescription.SignalsThe signal conventions are:xivLower-case nDenotes an active-LOW signal.Prefix HDenotes Advanced High-performance Bus (AHB) signals.Prefix PDenotes Advanced Peripheral Bus (APB) signals.Signal levelThe level of an asserted signal depends on whether the signal isactive-HIGH or active-LOW. Asserted means HIGH foractive-HIGH signals and LOW for active-LOW signals.Copyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

PrefaceFurther readingThis section lists publications by ARM Limited, and by third parties.ARM Limited periodically provides updates and corrections to its documentation. Seehttp://www.arm.com for current errata sheets, addenda, and the Frequently AskedQuestions list.ARM publicationsThis specification contains information that is specific to the protocol. See the followingdocuments for other relevant information: AMBA 3 APB Protocol Specification (ARM IHI 0024) AMBA AXI Protocol Specification (ARM IHI 0022) Multi-layer AHB Overview (ARM DVI 0045B).ARM IHI 0033ACopyright 2001, 2006 ARM Limited. All rights reserved.xv

PrefaceFeedbackARM Limited welcomes feedback on the AHB-Lite protocol and its documentation.Feedback on the protocolContact ARM Limited if you have any comments or suggestions about the AHB-Liteprotocol.Feedback on this specificationIf you have any comments on this specification, send email to errata@arm.com giving: the title the number the relevant page number(s) to which your comments apply a concise explanation of your comments.ARM Limited also welcomes general suggestions for additions and improvements.xviCopyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

Chapter 1IntroductionThis chapter provides an overview of the AHB-Lite protocol. It contains the followingsections: About the protocol on page 1-2 Operation on page 1-5 Multi-layer AHB-Lite on page 1-6.NoteFor illustrative purposes, a 32-bit data bus is used in this specification. Additional databus widths are permitted, as Data bus width on page 6-5 shows.ARM IHI 0033ACopyright 2001, 2006 ARM Limited. All rights reserved.1-1

Introduction1.1About the protocolAMBA AHB-Lite addresses the requirements of high-performance synthesizabledesigns. It is a bus interface that supports a single bus master and provideshigh-bandwidth operation.NoteSee Multi-layer AHB-Lite on page 1-6 for information about how to implement amulti-master system based on the AHB-Lite bus interface.AHB-Lite implements the features required for high-performance, high clockfrequency systems including: burst transfers single-clock edge operation non-tristate implementation wide data bus configurations, 64, 128, 256, 512, and 1024 bits.The most common AHB-Lite slaves are internal memory devices, external memoryinterfaces, and high bandwidth peripherals. Although low-bandwidth peripherals can beincluded as AHB-Lite slaves, for system performance reasons they typically reside onthe AMBA Advanced Peripheral Bus (APB). Bridging between this higher level of busand APB is done using a AHB-Lite slave, known as an APB bridge.Figure 1-1 shows a single master AHB-Lite system design with one AHB-Lite masterand three AHB-Lite slaves. The bus interconnect logic consists of one address decoderand a slave-to-master multiplexor. The decoder monitors the address from the master sothat the appropriate slave is selected and the multiplexor routes the corresponding slaveoutput data back to the master. :' 7 @ ''5 @'HFRGHU 6(/B 6(/B 6(/B 6ODYH 6ODYH 0DVWHU0XOWLSOH[RUVHOHFW6ODYH 5' 7 @ 5' 7 B 5' 7 B 5' 7 B Figure 1-1 AHB-Lite block diagram1-2Copyright 2001, 2006 ARM Limited. All rights reserved.ARM IHI 0033A

IntroductionNoteFigure 1-1 on page 1-2 does not show the master control signals. This is for clarity.The main component types of an AHB-Lite system are described in: Master Slave Decoder on page 1-4. Multiplexor on page 1-4.1.1.1MasterAn AHB-Lite master provides address and control information to initiate read and writeoperations. Figure 1-2 shows an AHB-Lite master interface.7UDQVIHU UHVSRQVH 5( ' 5(63*OREDO VLJQDOV 5(6(7Q &/.'DWD 5' 7 @ % /LWHPDVWHU ''5 @ :5,7( 6, ( @ %8567 @ 3527 @ 75 16 @ 0 67/2&. :' 7 @ GGUHVVDQG FRQWURO'DWDFigure 1-2 Master interface1.1.2SlaveAn AHB-Lite slave responds to transfers initiated by masters in the system. The slaveuses the HSELx select signal from the decoder to control when it responds to a bustransfer. The slave signals back to the master: the success failure or waiting of the data transfer.Figure 1-3 on page 1-4 shows an AHB-Lite slave interface.ARM IHI 0033ACopyright 2001, 2006 ARM Limited. All rights reserved.1-3

Introduction6HOHFW 6

required for AHB-Lite systems. Chapter 5 Slave Response Signaling Read this chapter for information about the slave response signaling. Chapter 6 Data Buses Read this chapter for information abou t the read and write data buses and how to interfac