Transcription

Nios II Gen2 Processor Reference GuideSubscribeSend FeedbackNII5V1GEN22015.04.02101 Innovation DriveSan Jose, CA 95134www.altera.com

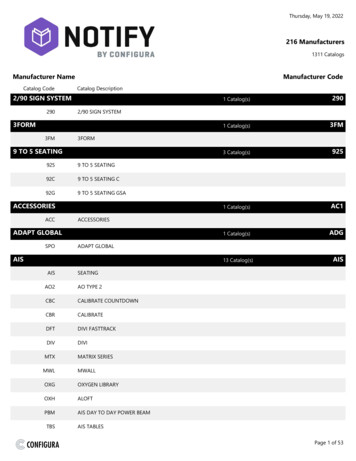

TOC-2ContentsIntroduction. 1-1Nios II Processor System Basics.1-1Getting Started with the Nios II Processor.1-2Customizing Nios II Processor Designs. 1-3Configurable Soft Processor Core Concepts. 1-4Configurable Soft Processor Core.1-4Flexible Peripheral Set and Address Map. 1-4Automated System Generation. 1-5OpenCore Plus Evaluation. 1-5Document Revision History. 1-6Processor Architecture. 2-1Processor Implementation.2-2Register File.2-3Arithmetic Logic Unit. 2-4Unimplemented Instructions. 2-4Custom Instructions. 2-4Floating-Point Instructions. 2-5Reset and Debug Signals. 2-9Exception and Interrupt Controllers.2-10Exception Controller. 2-10EIC Interface.2-11Internal Interrupt Controller. 2-11Memory and I/O Organization.2-12Instruction and Data Buses. 2-13Cache Memory. 2-15Tightly-Coupled Memory.2-16Address Map.2-17Memory Management Unit.2-17Memory Protection Unit. 2-18JTAG Debug Module. 2-19JTAG Target Connection.2-19Download and Execute Software. 2-20Software Breakpoints.2-20Hardware Breakpoints. 2-20Hardware Triggers. 2-20Trace Capture. 2-21Document Revision History.2-22Programming Model. 3-1Operating Modes. 3-1Altera Corporation

TOC-3Supervisor Mode. 3-1User Mode.3-2Memory Management Unit.3-2Recommended Usage. 3-2Memory Management.3-3Address Space and Memory Partitions.3-4TLB Organization. 3-5TLB Lookups.3-7Memory Protection Unit. 3-7Memory Regions. 3-8Overlapping Regions. 3-9Enabling the MPU. 3-9Registers.3-9General-Purpose Registers.3-9Control Registers.3-10Shadow Register Sets. 3-30Working with the MPU. 3-32MPU Region Read and Write Operations.3-33MPU Initialization. 3-33Debugger Access. 3-34Working with ECC. 3-34Enabling ECC. 3-34Handling ECC Errors. 3-34Injecting ECC Errors. 3-35Exception Processing.3-38Terminology. 3-38Exception Overview.3-38Exception Latency.3-41Reset Exceptions.3-41Break Exceptions.3-42Interrupt Exceptions.3-43Instruction-Related Exceptions. 3-46Other Exceptions.3-50Exception Processing Flow. 3-51Determining the Cause of Interrupt and Instruction-Related Exceptions. 3-54Handling Nested Exceptions. 3-56Handling Nonmaskable Interrupts. 3-58Masking and Disabling Exceptions. 3-58Memory and Peripheral Access. 3-60Cache Memory. 3-60Instruction Set Categories.3-61Data Transfer Instructions. 3-62Arithmetic and Logical Instructions. 3-62Move Instructions.3-63Comparison Instructions.3-63Shift and Rotate Instructions.3-64Program Control Instructions.3-65Other Control Instructions.3-66Custom Instructions.3-66Altera Corporation

TOC-4No-Operation Instruction. 3-67Potential Unimplemented Instructions. 3-67Document Revision History.3-67Instantiating the Nios II Gen2 Processor. 4-1Main Nios II Gen2 Tab. 4-1Vectors Tab.4-3Reset Vector. 4-3Exception Vector.4-4Fast TLB Miss Exception Vector.4-4Caches and Memory Interfaces Tab.4-5Instruction Cache.4-6Flash Accelerator.4-6Data Cache. 4-7Tightly-coupled Memories. 4-7Peripheral Region.4-7Arithmetic Instructions Tab.4-7Arithmetic Instructions.4-8Arithmetic Implementation. 4-8MMU and MPU Settings Tab. 4-9MMU. 4-10MPU.4-11JTAG Debug Tab. 4-11Advanced Features Tab.4-14ECC. 4-14Interrupt Controller Interfaces. 4-14Shadow Register Sets. 4-15Reset Signals.4-15CPU ID Control Register Value.4-15Generate Trace File.4-15Exception Checking.4-16Branch Prediction. 4-16RAM Memory Protection.4-16The Quartus II IP File.4-16Document Revision History.4-17Nios II Core Implementation Details. 5-1Device Family Support. 5-4Nios II/f Core.5-5Overview.5-5Arithmetic Logic Unit. 5-5Memory Access. 5-7Tightly-Coupled Memory.5-10Memory Management Unit.5-10Memory Protection Unit. 5-10Execution Pipeline. 5-11Instruction Performance.5-12Altera Corporation

TOC-5Exception Handling.5-13ECC. 5-14JTAG Debug Module.5-17Nios II/e Core. 5-17Overview. 5-17Arithmetic Logic Unit. 5-17Memory Access. 5-18Instruction Execution Stages.5-18Instruction Performance.5-18Exception Handling.5-19JTAG Debug Module.5-19Document Revision History.5-19Nios II Processor Revision History.6-1Nios II Versions.6-1Architecture Revisions. 6-1Core Revisions.6-2Nios II/f Core.6-2Nios II/e Core. 6-2JTAG Debug Module Revisions.6-2Document Revision History. 6-2Application Binary Interface. 7-1Data Types. 7-1Memory Alignment. 7-2Register Usage. 7-2Stacks. 7-4Frame Pointer Elimination. 7-4Call Saved Registers. 7-4Further Examples of Stacks. 7-5Function Prologues.7-6Arguments and Return Values.7-7Arguments.7-7Return Values. 7-8DWARF-2 Definition.7-9Object Files.7-9Relocation.7-9ABI for Linux Systems.7-12Linux Toolchain Relocation Information. 7-12Linux Function Calls. 7-16Linux Operating System Call Interface.7-16Linux Process Initialization. 7-17Linux Position-Independent Code.7-17Linux Program Loading and Dynamic Linking. 7-20Linux Conventions. 7-22Development Environment.7-23Document Revision History.7-23Altera Corporation

TOC-6Instruction Set Reference. 8-1Word Formats. 8-1I-Type. 8-1R-Type. 8-1J-Type.8-2Instruction Opcodes. 8-2Assembler Pseudo-Instructions. 8-4Assembler Macros.8-5Instruction Set Reference.8-5add .8-6addi .8-8and .8-10andhi . 8-10andi . 8-11beq . 8-12bge . 8-12bgeu.8-13bgt.8-14bgtu . 8-14ble . 8-15bleu .8-15blt .8-16bltu. 8-16bne .8-17br . 8-18break . 8-19bret . 8-20call . 8-20callr .8-21cmpeq .

larger collection of documents covering the Nios II processor and its usage that you can find on the Literature: Nios II Processor Page of the Altera website. Nios II Processor System Basics The Nios II processor is a general-purpose RISC processor core with the following features: Full 32-bit instruction set, data path, and address space