Transcription

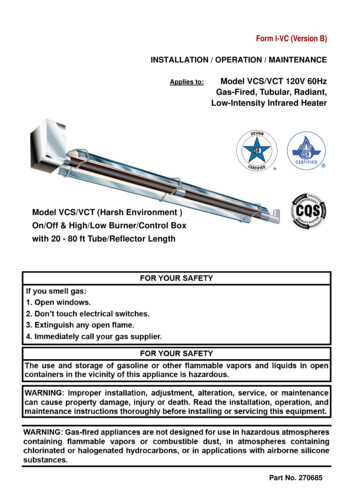

VCS MX/VCS MXi UserGuideVersion D-2010.06June 2010Comments?E-mail your comments about this manual to:vcs support@synopsys.com.

Copyright Notice and Proprietary InformationCopyright 2010 Synopsys, Inc. All rights reserved. This software and documentation contain confidential andproprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under alicense agreement and may be used or copied only in accordance with the terms of the license agreement. No part ofthe software and documentation may be reproduced, transmitted, or translated, in any form or by any means,electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or asexpressly provided by the license agreement.Right to Copy DocumentationThe license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee mustassign sequential numbers to all copies. These copies shall contain the following legend on the cover page:This document is duplicated with the permission of Synopsys, Inc., for the exclusive use ofand its employees. This is copy number .”Destination Control StatementAll technical data contained in this publication is subject to the export control laws of the United States of America.Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader’s responsibility todetermine the applicable regulations and to comply with them.DisclaimerSYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITHREGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OFMERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.Registered Trademarks ( )Synopsys, AMPS, Cadabra, CATS, CRITIC, CSim, Design Compiler, DesignPower, DesignWare, EPIC, Formality,HSIM, HSPICE, iN-Phase, in-Sync, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Photolynx, PhysicalCompiler, PrimeTime, SiVL, SNUG, SolvNet, System Compiler, TetraMAX, VCS, Vera, and YIELDirector are registeredtrademarks of Synopsys, Inc.Trademarks ( )AFGen, Apollo, Astro, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, Columbia, Columbia-CE, Cosmos,CosmosEnterprise, CosmosLE, CosmosScope, CosmosSE, DC Expert, DC Professional, DC Ultra, Design Analyzer,Design Vision, DesignerHDL, Direct Silicon Access, Discovery, Encore, Galaxy, HANEX, HDL Compiler, Hercules,Hierarchical Optimization Technology, HSIMplus, HSPICE-Link, iN-Tandem, i-Virtual Stepper, Jupiter, Jupiter-DP,JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Magellan, Mars, Mars-Xtalk, Milkyway,ModelSource, Module Compiler, Planet, Planet-PL, Polaris, Power Compiler, Raphael, Raphael-NES, Saturn,Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, Taurus, TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, andVMC are trademarks of Synopsys, Inc.Service Marks (SM)MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.SystemC is a trademark of the Open SystemC Initiative and is used under license.ARM and AMBA are registered trademarks of ARM Limited.Saber is a registered trademark of SabreMark Limited Partnership and is used under license.All other product or company names may be trademarks of their respective owners.ii

Contents1. Getting StartedVCS MX Support with Technologies . . . . . . . . . . . . . . . . . . . . . .1-2Setting Up VCS MX. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4Verifying Your System Configuration . . . . . . . . . . . . . . . . . . .1-4Obtaining a License . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5Setting Up Your Environment. . . . . . . . . . . . . . . . . . . . . . . . .1-7Setting Up Your C Compiler. . . . . . . . . . . . . . . . . . . . . . . . . .1-8Creating a synopsys sim.setup File . . . . . . . . . . . . . . . . . . .The Concept of a Library In VCS MX . . . . . . . . . . . . . . . .Library Name Mapping . . . . . . . . . . . . . . . . . . . . . . . . . .Including Other Setup Files . . . . . . . . . . . . . . . . . . . . . . .Using SYNOPSYS SIM SETUP Environment Variable .1-91-111-111-121-13Displaying Setup Information . . . . . . . . . . . . . . . . . . . . . . . . .1-13Displaying Design Information Analyzed Into a Library . . . . .1-14Using VCS MX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-16Basic Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-17Default Time Unit and Time Precision . . . . . . . . . . . . . . . . . . . . .1-18iii

2. VCS MX FlowAnalysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2Using vhdlan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Commonly Used Analysis Options . . . . . . . . . . . . . . . . . .2-32-3Using vlogan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Commonly Used Analysis Options . . . . . . . . . . . . . . . . . .2-62-6Analyzing the Design to Different Libraries . . . . . . . . . . . . . .2-13Elaboration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13.2-13Using vcs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Commonly Used Options . . . . . . . . . . . . . . . . . . . . . . . . .2-142-15Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-18Interactive Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-18Batch Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-19Commonly Used Runtime Options. . . . . . . . . . . . . . . . . . . . .2-193. Elaborating the DesignivElaborating the Design in Debug Mode. . . . . . . . . . . . . . . . . . . .3-1Elaborating the Design in Optimized Mode . . . . . . . . . . . . . . . . .3-2Key Elaboration Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3Initializing Verilog Memories and Registers . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-33-5Overriding Generics and Parameters . . . . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-63-7Checking for X and Z Values In Conditional Expressions . . .3-8

Enabling the Checking . . . . . . . . . . . . . . . . . . . . . . . . . . .Filtering Out False Negatives . . . . . . . . . . . . . . . . . . . . . .3-93-10Cross Module References (XMRs) . . . . . . . . . . . . . . . . . . . .hdl xmr Procedure and hdl xmr System Task. . . . . . . .Data Types Supported . . . . . . . . . . . . . . . . . . . . . . . . . . .VHDL Referencing Verilog using hdl xmr procedure. . . .Verilog Referencing VHDL objects using hdl xmr . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . hdl xmr Support for VHDL Variables . . . . . . . . . . . . . . .Datatype Support and Usage Examples . . . . . . . . . . . . .3-123-133-133-143-163-173-183-19VCS MX V2K Configurations and Libmaps . . . . . . . . . . . . . .Library Mapping Files . . . . . . . . . . . . . . . . . . . . . . . . . . . .Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-243-253-263-303-30Using evalorder Option . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-364. Simulating the DesignUsing DVE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2Using UCLI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ucli2Proc Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-34-5Options for Debugging Using DVE and UCLI . . . . . . . . . . . . . . .4-6Key Runtime Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8Overriding Generics at Runtime. . . . . . . . . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-84-9Passing Values from the Runtime Command Line . . . . . . . .4-13v

5. VCS Multicore TechnologyApplication Level ParallelismVCS Multicore Technology Options . . . . . . . . . . . . . . . . . . . . . . .5-16Use Model for Assertion Simulation. . . . . . . . . . . . . . . . . . . .5-18Use Model for Toggle and Functional Coverage . . . . . . . . . .5-18Use Model for VPD Dumping. . . . . . . . . . . . . . . . . . . . . . . . .5-18Running VCS Multicore Simulation . . . . . . . . . . . . . . . . . . . . . . .5-19Assertion Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19Toggle Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-20Functional Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-21VPD File. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23Parallel SAIF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24Customary SAIF System Function Entries. . . . . . . . . . . . . . .5-24Enabling Parallel SAIF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-256. VPD, VCD, and EVCD UtilitiesviAdvantages of VPD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2Dumping a VPD File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3Using System Tasks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Enable and Disable Dumping. . . . . . . . . . . . . . . . . . . . . .Override the VPD Filename . . . . . . . . . . . . . . . . . . . . . . .Dump Multi-dimensional Arrays and Memories . . . . . . . .Using vcdplusmemorydump . . . . . . . . . . . . . . . . . . . . . .Capture Delta Cycle Information . . . . . . . . . . . . . . . . . . .6-36-46-86-96-206-20Dumping an EVCD File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-21

Post-processing Utilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-23The vcd2vpd Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Options for specifying EVCD options . . . . . . . . . . . . . . . .6-246-26The vpd2vcd Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .The Command File Syntax. . . . . . . . . . . . . . . . . . . . . . . .6-276-34The vpdmerge Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-387. Performance TuningCompile-time Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-2Incremental Compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3Compile Once and Run Many Times . . . . . . . . . . . . . . . . . . .7-4Parallel Compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4Runtime Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5Using Radiant Technology . . . . . . . . . . . . . . . . . . . . . . . . . . .Compiling With Radiant Technology. . . . . . . . . . . . . . . . .Applying Radiant Technology to Parts of the Design . . . .7-57-67-6Improving Performance When Using PLIs. . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-167-17Impact on Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-208. Gate-level SimulationSDF Annotation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2Using Unified SDF Feature . . . . . . . . . . . . . . . . . . . . . . . . . .8-2Using sdf annotate System Task. . . . . . . . . . . . . . . . . . . . .8-3Delays and Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-5Transport and Inertial Delays. . . . . . . . . . . . . . . . . . . . . . . . .8-6vii

viiiDifferent Inertial Delay Implementations . . . . . . . . . . . . .Enabling Transport Delays . . . . . . . . . . . . . . . . . . . . . . . .8-78-10Pulse Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-11Pulse Control with Transport Delays . . . . . . . . . . . . . . . . . . .Pulse Control with Inertial Delays. . . . . . . . . . . . . . . . . . .Specifying Pulse on Event or Detect Behavior . . . . . . . . .8-138-158-19Specifying the Delay Mode . . . . . . . . . . . . . . . . . . . . . . . . . .8-24Using the Configuration File to Disable Timing . . . . . . . . . . . . . .8-26Using the timopt Timing Optimizer . . . . . . . . . . . . . . . . . . . . . . .8-26Editing the timopt.cfg File . . . . . . . . . . . . . . . . . . . . . . . . . . .Editing Potential Sequential Device Entries . . . . . . . . . . .Editing Clock Signal Entries . . . . . . . . . . . . . . . . . . . . . . .8-298-298-30Using Scan Simulation Optimizer . . . . . . . . . . . . . . . . . . . . . . .8-31ScanOpt Config File Format . . . . . . . . . . . . . . . . . . . . . . . . .8-32ScanOpt Assumptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-33Negative Timing Checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-34The Need for Negative Value Timing Checks . . . . . . . . . . . .The setuphold Timing Check Extended Syntax . . . . . . .Negative Timing Checks for Asynchronous Controls . . . .The recrem Timing Check Syntax . . . . . . . . . . . . . . . . .8-358-408-448-44Enabling Negative Timing Checks . . . . . . . . . . . . . . . . . . . . .8-47Other Timing Checks Using the Delayed Signals . . . . . . . . .8-49Checking Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-53Toggling the Notifier Register. . . . . . . . . . . . . . . . . . . . . . . . .8-54SDF Back-annotation to Negative Timing Checks . . . . . . . . .8-55How VCS MX Calculates Delays . . . . . . . . . . . . . . . . . . . . . .8-56

Using Multiple Non-overlapping Violation Windows. . . . . . . .8-58Using VITAL Models and Netlists . . . . . . . . . . . . . . . . . . . . . . . .8-63Validating and Optimizing a VITAL Model . . . . . . . . . . . . . . .Validating the Model for VITAL Conformance . . . . . . . . .Verifying the Model for Functionality . . . . . . . . . . . . . . . .Optimizing the Model for Performance and Capacity. . . .Re-Verifying the Model for Functionality. . . . . . . . . . . . . .Understanding Error and Warning Messages . . . . . . . . .Distributing a VITAL Model. . . . . . . . . . . . . . . . . . . . . . . .8-638-648-648-658-668-668-67Simulating a VITAL Netlist . . . . . . . . . . . . . . . . . . . . . . . . . . .Applying Stimulus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Overriding Generic Parameter Values . . . . . . . . . . . . . . .Understanding VCS MX Error Messages. . . . . . . . . . . . .Viewing VITAL Subprograms . . . . . . . . . . . . . . . . . . . . . .Timing Back-annotation . . . . . . . . . . . . . . . . . . . . . . . . . .VCS MX Naming Styles . . . . . . . . . . . . . . . . . . . . . . . . . .Negative Constraints Calculation (NCC) . . . . . . . . . . . . .Simulating in Functional Mode . . . . . . . . . . . . . . . . . . . . .8-688-688-688-708-718-718-718-728-73Understanding VITAL Timing Delays and Error Messages . .Negative Constraint Calculation (NCC) . . . . . . . . . . . . . .Conformance Checks. . . . . . . . . . . . . . . . . . . . . . . . . . . .Error Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-758-758-758-789. CoverageCode Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1Functional Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-2Options For Coverage Metrics . . . . . . . . . . . . . . . . . . . . . . . . . .9-3ix

10. Using SystemVerilogUsage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2Using VMM with SV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-3Debugging SystemVerilog Designs . . . . . . . . . . . . . . . . . . . . . . .10-4Functional Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4Memory Profiler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-6Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-6Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-7Memory Profile Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-8SystemVerilog Bounded Queues . . . . . . . . . . . . . . . . . . . . . . . .10-13Support for wait() Statement with a Static Class Member Variable 10-15xParameters and Localparams in Classes . . . . . . . . . . . . . . . . . .10-15Support for Verilog 1364-2005 Math Functions. . . . . . . . . . . . . .10-16Single-Sized Packed Dimension Extension . . . . . . . . . . . . . . . .10-17Streaming Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Packing (Used on RHS) . . . . . . . . . . . . . . . . . . . . . . . . . .Unpacking (Used on LHS) . . . . . . . . . . . . . . . . . . . . . . . .Packing and Unpacking . . . . . . . . . . . . . . . . . . . . . . . . . .Propagation and force Statement. . . . . . . . . . . . . . . . . . .Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Structures with Streaming Operators . . . . . . . . . . . . . . . .10-1910-1910-2010-2010-2110-2110-21Extensions to SystemVerilog . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-21Unique/Priority Case/IF Final Semantic Enhancements . . . .10-22

Using Unique/Priority Case/If with Always Block or ContinousAssign . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-23Using Unique/Priority Inside a Function . . . . . . . . . . . . . . 10-26System Tasks to Control Warning Messages . . . . . . . . . . 10-2911. Using OpenVera Native TestbenchUsage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-3Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Importing VHDL Procedures . . . . . . . . . . . . . . . . . . . . . .Exporting OpenVera Tasks. . . . . . . . . . . . . . . . . . . . . . . .Using Template Generator . . . . . . . . . . . . . . . . . . . . . . .Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-311-611-711-811-911-11Key Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-23Multiple Program Support . . . . . . . . . . . . . . . . . . . . . . . . . . .Configuration File Model . . . . . . . . . . . . . . . . . . . . . . . . .Configuration File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Usage Model for Multiple Programs . . . . . . . . . . . . . . . . .NTB Options and the Configuration File. . . . . . . . . . . . . .11-2411-2411-2411-2611-27Separate Compilation of Testbench Files . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-2811-3011-31Class Dependency Source File Reordering. . . . . . . . . . . . . .Circular Dependencies . . . . . . . . . . . . . . . . . . . . . . . . . . .Dependency-based Ordering in Encrypted Files . . . . . . .11-3111-3311-34Using Encrypted Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-34Functional Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-35Using Reference Verification Methodology . . . . . . . . . . . . . .11-35xi

Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-37Memory Profiler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .UCLI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .VCS MX Dynamic Memory Profile Report . . . . . . . . . . . .11-3711-3811-3811-3912. Aspect Oriented ExtensionsAspect-Oriented Extensions in SV. . . . . . . . . . . . . . . . . . . . .12-3Processing of AOE as a Precompilation Expansion . . . . . . .Weaving advice into the target method . . . . . . . . . . . . . .12-612-11Pre-compilation Expansion details. . . . . . . . . . . . . . . . . . . . .Precedence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1612-1713. Using ConstraintsxiiConstraints Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-2Using Constraint Profiling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-3Controlling Constraint Profiling . . . . . . . . . . . . . . . . . . . . . . .13-4Using the Constraint Profiling Report . . . . . . . . . . . . . . . . . . . . .13-5Using the Hierarchical Constraint Debugger Report . . . . . . . . . .Color Coding Constraint Blocks and rand vars . . . . . . . .Avoiding Duplicate Printing of Original Constraint Set . . .13-613-713-7Extracting Test Cases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-9Specifying Test Case Extraction Switches . . . . . . . . . . . . . . .Constraint Test Case Extraction Examples . . . . . . . . . . .Constraint Extraction Switch Usage Notes. . . . . . . . . . . .Constraints Directory Structure . . . . . . . . . . . . . . . . . . . .13-1113-1213-1313-14

Backward Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . .13-14Test Case Extraction Features. . . . . . . . . . . . . . . . . . . . . . . .13-15Constraint Guard Error Suppression . . . . . . . . . . . . . . . . . . . . . .13-17Error Message Suppression Limitations . . . . . . . . . . . . . . . .Flattening Nested Guard Expressions . . . . . . . . . . . . . . .Pushing Guard Expressions into Foreach Loops . . . . . . .13-1813-1813-19Array and XMR Support in std::randomize() . . . . . . . . . . . . . . . .Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-2013-22XMR Support in Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-23XMR Function Calls in Constraints . . . . . . . . . . . . . . . . . . . .13-25State Variable Index in Constraints . . . . . . . . . . . . . . . . . . . . . . .13-26Runtime Check for State Versus Random Variables . . . . . . .13-26Array Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-2714. Extensions for SystemVerilog CoverageSupport for Reference Arguments in get coverage() . . . . . . . . .14-29get inst coverage() method . . . . . . . . . . . . . . . . . . . . . . . . .14-30get coverage() method . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-30Functional Coverage Methodology Using the SystemVerilog C/C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-31SystemVerilog Functional Coverage Flow . . . . . . . . . . . . . . .14-32Covergroup Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .SystemVerilog (Covergroup for C/C ): covg.sv . . . . . . .C Testbench: test.c. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Approach #1: Passing Arguments by Reference . . . . . . .Approach #2: Passing Arguments by Value . . . . . . . . . . .14-3314-3514-3514-3514-35xiii

Compile Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Runtime . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-3614-36C/C Functional Coverage API Specification . . . . . . . . . . .14-3615. OpenVera-SystemVerilog Testbench InteroperabilityxivScope of Interoperability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-2Importing OpenVera types into SystemVerilog . . . . . . . . . . . . . .15-3Data Type Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-6Mailboxes and Semaphores . . . . . . . . . . . . . . . . . . . . . . . . .15-7Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-10Strings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-10Enumerated Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-10Integers and Bit-Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-13Arrays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-13Structs and Unions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-15Connecting to the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-16Mapping Modports to Virtual Ports. . . . . . . . . . . . . . . . . . . . .Virtual Modports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Importing Clocking Block Members into a Modport . . . . .15-1615-1615-17Semantic Issues with Samples, Drives, and Expects . . . . . .15-23Notes to Remember . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Blocking Functions in OpenVera . . . . . . . . . . . . . . . . . . .Constraints and Randomization . . . . . . . . . . . . . . . . . . .Functional Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-2315-2315-2415-24Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-25

Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-2716. Using SystemVerilog AssertionsUsing SVAs in the HDL Design . . . . . . . . . . . . . . . . . . . . . . . . . .16-2Using Standard Checker Library . . . . . . . . . . . . . . . . . . . . . .Instantiating SVA Checkers in Verilog . . . . . . . . . . . . . . .Instantiating SVA Checkers in VHDL . . . . . . . . . . . . . . . .16-216-316-4Inlining SVAs in the Verilog Design . . . . . . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-616-7Inlining SVA in the VHDL design . . . . . . . . . . . . . . . . . . . . . .Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-816-9Controlling SystemVerilog Assertions . . . . . . . . . . . . . . . . . . . . .16-10Elaboration and Runtime Options . . . . . . . . . . . . . . . . . . . . .16-11Assertion Monitoring System Tasks . . . . . . . . . . . . . . . . . . . .16-14Using Assertion Categories . . . . . . . . . . . . . . . . . . . . . . . . . .Using OpenVera Assertion System Tasks . . . . . . . . . . . .Using Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Stopping and Restarting Assertions By Category . . . . . .16-1716-1816-1916-20Viewing Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-25Using a Report File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-2517. Using Property Specification LanguageIncluding PSL in the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-2Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-2Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-4Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-4xv

Using SVA Options, SVA System Tasks, and OV Classes . .17-5Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-618. Using SystemCOverview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-4Verilog Design Containing Verilog/VHDL Modules and SystemC LeafModules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-6Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-7Input Files Required. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Generating Verilog/VHDL Wrappers for SystemC Modules18-818-9Supported Port Data Types . . . . . . . . . . . . . . . . . . . . . . . . . .18-12Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-14Controlling Time Scale and Resolution in a SystemC . . . . . .Automatic adjustment of the time resolution . . . . . . . . . .Setting time scale/resolution of Verilog/VHDL kernel . . . .Setting time scale/resolution of SystemC kernel . . . . . . .18-1718-1818-1818-19Adding a Main Routine for Verilog-On-Top Designs . . . . . . .18-20SystemC Designs Containing Verilog and VHDL Modules . . . . .18-21Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-22Input Files Required. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Generating a SystemC Wrapper for Verilog Modules . . .Generating A SystemC Wrapper for VHDL Design . . . . .18-2318-2418-25Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-28Elaboration Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-31VHDL Design Containing Verilog/VHDL Modules and SystemC LeafModules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-34xvi

Usage Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-34Input Files Required. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-35Generating a Verilog/VHDL Wrapper for SystemC Modules 18-36Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Use Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-3918-41Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-41Parameters in Verilog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-42Parameters in VHDL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-4

electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement. Right to Copy Documentation The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only.