Transcription

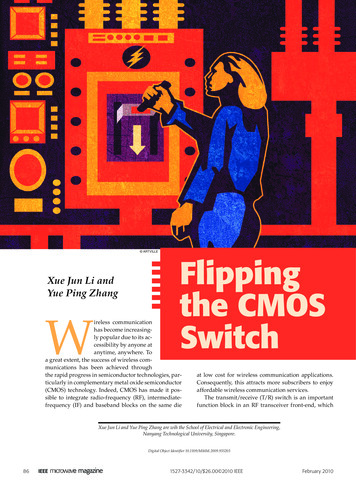

ARTVILLEXue Jun Li andYue Ping ZhangWFlippingthe CMOSSwitchireless communicationhas become increasingly popular due to its accessibility by anyone atanytime, anywhere. Toa great extent, the success of wireless communications has been achieved throughthe rapid progress in semiconductor technologies, particularly in complementary metal oxide semiconductor(CMOS) technology. Indeed, CMOS has made it possible to integrate radio-frequency (RF), intermediatefrequency (IF) and baseband blocks on the same dieat low cost for wireless communication applications.Consequently, this attracts more subscribers to enjoyaffordable wireless communication services.The transmit/receive (T/R) switch is an importantfunction block in an RF transceiver front-end, whichXue Jun Li and Yue Ping Zhang are wih the School of Electrical and Electronic Engineering,Nanyang Technological University, Singapore.Digital Object Identifier 10.1109/MMM.2009.935203861527-3342/10/ 26.00 2010 IEEEFebruary 2010

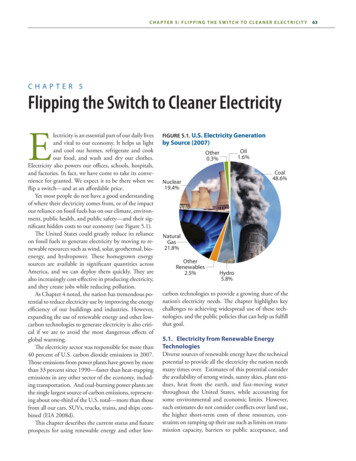

generally consists of one transmission branchTABLE 1. Summary of wireless technologies.and one reception branch [1]. Along the reception branch, the received RF signals will beSystem Characteristicspassed through a bandpass filter (BPF) and thenFrequency Date Rate Peak Power Duplexingswitched by a T/R switch to a low-noise ampli(Mb/s)Level (dBm) FeaturesTechnology (GHz)fier (LNA); while in the transmission branch,the transmitted RF signals will be amplified by2G0.9/1.8/1.9 0.130FDDa power amplifier (PA), and then switched by3G1.8 2.2 230FDD/TDDthe T/R switch to the antenna. In particular, aT/R switch can be found in any time-division4G LTE2.0 2.6 5030FDD/TDDduplexing (TDD)-based radio front-end [1], and4G WiMAX2.3 3.5 7530FDD/TDDit connects radio transmitter (TX) and receiverBluetooth2.4 5420TDD(RX) alternatively to a shared antenna (ANT). ATDD radio system can inherently offer a numberWLAN2.4 or 5.8 5420TDDof advantages and flexibilities that a frequencyUWB3.1 10.6 110TDD215division duplexing (FDD) radio system cannot.60-GHz57 66 150010TDDThese advantages include channel reciprocity,dynamic bandwidth allocation, and higher freon the IEEE 802.11 standard [9]. Wireless personal areaquency diversity [2]. As shown in Table 1, TDD is domnetworks (WPAN) are based on Bluetooth [10], andinant in area-network radio systems and is expandingultra-wide band (UWB) [11] and 60-GHz standards [12]its share in cellular radio systems.have been developed for short-range, high-speed perThe difficulty of integrating various RF composonal wireless communications [3]. Table 1 lists somenents in a single chip is dependent on the wirelessdata on these radio systems related to design of T/Rtechnology requirements. For example, wireless comswitches. It is interesting to note that, as these radiomunications are mainly realized with cellular andsystems evolve, their operating frequencies get higherarea-network radio systems [3]. First generation (1G)and bandwidths get wider due to the congestion incellular radio systems began operation in 1979, usinglower frequency bands and the increase in data rates.analog signals, FDD, and frequency division multipleIt is more important to note that the maximal transmitaccess (FDMA) [4]. In the early 1990s, second generapower levels are 30 dBm and 20 dBm for cellular andtion (2G) cellular radio systems arrived, which employWLAN radio terminals, respectively.digital signals, FDD, and time division multiple accessFrom Table 1, we notice that the operating fre(TDMA) or code division multiple access (CDMA) toquency increases as the wireless technology advances.provide telephony plus text messaging and limitedConsequently, it is desirable to have a high level ofcircuit-switched data communications [5]. 2G systemsintegration using CMOS technology so that we canachieved unexpected success, brought the niche 1G tosqueeze more functions onto the same wireless comthe mass market, and revolutionized the world communication device. However, CMOS has not yet realmunications. In 2001, following the phenomenal sucized complete cellular radio integration because ofcess of 2G, third generation (3G) cellular radio systemschallenges in PA and T/R switches. These challengesdebuted. Since then, 3G systems have been deployedbecome even tougher as CMOS scales. Nevertheless,in many countries, using FDD or TDD and widebandmany techniques have been proposed to mitigate theW-CDMA or time division-synchronous CDMA (TDdifficulty on the PA integration [13]. In this article, weSCDMA) to allow mobile multimedia applications [6],focus on design of T/R switches in CMOS and review[7]. The fourth generation (4G) work started in 2005 andtheir recent advances. The following section describesoffers a high degree of commonality of functionalitytypical T/R switch topologies, key performanceworldwide, while retaining the flexibility to supportparameters, and n-channel MOS (NMOS) field-effecta wide range of services and applications (100 Mb/stransistor (FET) device circuit models. That is followedfor high mobility and 1 Gb/s for low mobility), andby a discussion of the important circuit techniques anddoes so in a cost-efficient manner. It is expected thatconcepts developed specifically for improving the per4G candidate technologies can be approved in Octoberformance of CMOS T/R switches. Finally, the reported2010. The two most likely 4G candidate technologiesCMOS T/R switches and identification of the imporare mobile worldwide interoperability for microwavetant work for future development is summarized.access (WiMAX) and long-term evolution (LTE) [8].Both 4G candidate technologies feature multi-input/multi-output (MIMO) antennae to improve spectralT/R Switch Topologies andefficiency and transmission quality.Device Circuit ModelsMeanwhile, various area-network radio systems,The aforementioned T/R switch, whose function is tosuch as wireless local area network (WLAN), are basedalternately connect between the antenna and the TXFebruary 201087

ANTTXM1M2RG1VcRXRG2VcFigure 1. Series single-pole double-throw transmit/receiveswitch topology.or RX, can be implemented using mechanical switchesor solid-state switches. However, as compared withmechanical switches, solid-state switches have thefollowing advantages: 1) faster switching speedor lower switching time, 2) higher reliability, and,most importantly, 3) more compact size and, therefore, easier use in large-scale integration/fabrication. Micromachining provides new technologies,such as RF microelectromechanical systems (MEMS)[14] to implement T/R switches, but integration andreliability challenges have prevented these solutionsfrom being adopted. Solid-state switches can be implemented using positive intrinsic negative (PIN) diodes[15], FETs/high electromobility transistors (HEMTs)[16] and CMOS transistors, where PIN diodes andFETs/HEMTs are fabricated using gallium arsenide(GaAs) technology.As compared to other technologies used for RFand microwave control functions (e.g., GaAs), CMOStechnology is superior due to its low-cost structureand its integration potential of IF and baseband blockson the same die [17]. In particular, CMOS transceivers can provide lower power consumption, lowercomponent cost, and stability in manufacturing,comparable to other digital CMOS products. Investigation into the design of T/R switches in CMOSstarted in the late 1990s. Caverly reported a CMOST/R switch design with less than 1-dB insertionloss and isolation of greater than 50 dB [17]. Madihian et al. presented a CMOS RF IC design for 900MHz–2.4 GHz band wireless communication networks in [18]. Following that, many design techniques for CMOS RF switches have been reported.This article focuses on the design of T/R switchesusing CMOS technology.The performance of a T/R switch is quantified bythe following [19]: Insertion loss: the signal power loss introduced bythe T/R switch between the input port and theoutput port Isolation: how well a T/R switch is able to preventpower leakage from the input port to ports otherthan the desired output port Linearity: the property of an active circuit devicethat its output power linearly increases with its88input power; in practice, nonlinearity is usuallymeasured by checking the third-order interceptpoint (IP3), which relates nonlinear productscaused by the third-order nonlinear term to thelinear term Power handling capacity: usually measured by the1-dB compression point (P1dB), which is defined asthe input power that causes a 1 dB drop in the linear gain due to device saturation. P1dB can also beconsidered as an indicator of nonlinearity; however, it is not as useful as IP3 because a T/R switchis designed to have insertion loss less than 1 dB.In addition, the inband third-order (and sometimes higher-order) intermodulation distortionis the important issue, because these nonlinearities can severely affects performance even beforecompression occurs Offset: measures the nonzero output voltage of adevice when its input port is grounded Switching time: the delay between the signal at theoutput port and that at the input port, which isintroduced by a T/R switch.Generally, a T/R switch should be designed to havelow insertion loss, high isolation, large P1dB, low offset,short switching time, and good reliability. For a mobilecellular radio, the T/R switch should achieve an insertion loss of less than 1.5 dB, an isolation of more than30 dB, and a P1dB of more than 33 dBm. For a WLANradio, the specifications for the switch are typically aninsertion loss of less than 1 dB, an isolation of morethan 20 dB, and a P1dB of more than 23 dBm. Usually, switching time is not a limiting factor for mobilecellular and WLAN radios because the typical valueof switching time requirements for WLAN radios is10 ms and the typical value of CMOS T/R switchingtime is 0.1 ms [20].Another important issue related to CMOS T/Rswitches is electrostatic discharge. As CMOS scales,gate oxide thickness continues to decrease andCMOS circuits become more vulnerable to the ubiquitous electrostatic discharge, especially due to thefact that a static charge transfer occurs upon staticelectricity discharge between a human and a chip.The standard human-body model assumes a staticcharge transfer of about 0.1 µC upon static electricity discharge between a human and a chip. Suchcharge may result in a tremendous electric field inthe gate oxide on the order of 1015 V/m because thegate oxide thickness is only about 1028 m. The T/Rswitch is conventionally connected to the outsideworld through the antenna and can therefore beexposed to electrostatic discharge stress events. It isthus desirable to incorporate a sufficient level of onchip electrostatic discharge protection on a givenT/R switch circuit. For example, an on-chip inductor shunt between the input/output and ground canprovide electrostatic discharge protection, tune outFebruary 2010

the parasitic capacitance so as to further decreaseinsertion loss, and serve as one part of the impedance matching network for further integrationwith other RF components, such as LNA and PA.In particular, as the gate control pins for integratedT/R switches are connected on-chip, electrostaticdischarge is usually implemented at the port ofthe antenna. On the contrary, if the T/R switch isfabricated on a separate chip apart from other RFcomponents, the gate-control pins are usually connected off-chip and electrostatic discharge shouldbe implemented for the T/R switch chip.The gate resistance RG improves dc bias isolationand NMOS transistor reliability. If RG is not present,the fluctuations of VGD and VGS of the NMOS transistor due to the voltage swing at its drain and sourcewill be higher, which not only affects the NMOStransistor channel resistance, but also may result inexcessive voltage across the gate dielectric and causebreakdown. In addition, RG also affects power handling and frequency response of the T/R switch.Higher RG values provide better dc isolation on thegate and improve low-end frequency response, butat the expense of slower switching times because thegate capacitance must be charged/discharged throughhigher RG values [21]. Thus, a typical range of valuesfor RG is 5–15 kV. It is worth pointing out that the gateresistance RG is typically implemented using an onchip resistor.TopologiesTABLE 2. Typical values of Vth versus gate widthfor NMOS.Gate Width (µm)0.250.180.130.090.065Vth (V)0.470.4450.440.430.422function while the shunt transistors, M3 and M4, are usedto pull the undesired signal in each mode to ground asM3 and M4 are turned ON when M1 and M2 are turnedOFF, respectively. As compared with the series topology, the series-shunt topology improves isolation butincreases insertion loss, especially at high frequencies.Modified SPDT T/R Switch TopologiesFigure 3 shows a differential SPDT T/R switch topology [22], [23], which is mirrored from the single-endedseries SPDT T/R switch topology shown in Figure 1.Theoretically, differential topology has 3-dB higherpower-handling capability than single-ended topology. As the power-handling capability is a bottleneckof CMOS T/R switches, differential topology is of greatadvantage in current CMOS technology. Furthermore,the differential nature permits higher linearity andlower offset and makes it immune to power supplyvariations and substrate noise. Therefore, differentialANTM1TXA survey of literature reveals that various CMOST/R switch topologies have been proposed. They aredescribed in the following sections.Series SPDT T/R Switch TopologyFigure 1 shows a series T/R switch topology. It adoptstransistor M1 for the TX path and another transistorM 2 for the RX path. A control signal is applied to thegate of a transistor to alternate its ON/OFF state. Forexample, during a transmitting period, Vc is high andM1 is turned ON; at the same time, Vc is low and M 2is turned OFF. In this way, the ANT is connected tothe TX path. On the contrary, M1 is turned OFF andM 2 is turned ON during a receiving period, letting theANT connected to the RX path. Therefore, this T/Rswitch illustrates a typical single-pole double-throw(SPDT) configuration. Note that Vc and Vc are belowand above, respectively, the device threshold voltageVth, which is generally determined by many factors,such as gate width, oxide thickness, and temperature.Table 2 lists the typical values of Vth (,0.5 V) versusvalues of gate width for NMOS.M2RG1RG2RG3M3RXRG4M4VcVcFigure 2. Series-shunt single-pole double-throw transmit/receive switch topology.ANT TX M1M2RG1RG2RG3RG4VcTX–RX VcM3M4RX–ANT–Series-Shunt SPDT T/R Switch TopologyFigure 2 shows a series-shunt T/R switch topology.The series transistors, M1 and M2, perform the switchFebruary 2010Figure 3. Differential single-pole double-throw transmit/receive switch topology [23].89

RXSteppedImpedanceRG2as 33 dBm while the received signal from the antennais typically less than 230 dBm [2], [24]–[27].4P4T T/R Switch TopologyMIMO technology has emerged as a promising solution to challenges in 4G systems [28]. MIMO technology, however, shifts the paradigm in which the T/RVcswitch functions. It utilizes multiple antennae to attainM1RG1true full duplexing and, therefore, does not require theswitch to specify the transmitting or receiving operaTXtions. The role of a T/R switch is to link data streams totheir corresponding antennae. The number of antennaFigure 4. Asymmetric single-pole double-throw transmit/elements used in a MIMO radio dictates the configurareceive switch topology.tion of the T/R switch. The antenna elements for a basestation should be limited to a moderate number suchas four, because large RF output powers can pose envitopology is normally preferred in applications requirronmental concerns and may be a public health threating higher signal quality.[29], [30]. In addition, a maximum of four dual polarFigure 4 shows an asymmetric SPDT T/R switchized patch antennae with half-wavelength spacing cantopology, which can be considered as a modificationbe exploited for terminal operations. However, thereto the symmetric series-shunt T/R switch topologyare concerns that space constraints in handsets mayshown in Figure 2 by replacing transistor M2 in the RXpose a challenge to the use of more than one antenna.path with a stepped impedance block (see the “SteppedNevertheless, we believe that four antenna elementsImpedance” section for more details) and deletingare proper for most MIMO radios.transistor M3 in the TX side. The stepped impedA four-pole and four-throw (4P4T) T/R switchance block exhibits high impedance in the TX modetopology has been proposed for MIMO radios withbut low impedance in the RX mode. The asymmetricfour antenna elements [31]. Figure 5 shows the 4P4TT/R switch topology meets the different requirementstopology, which exhibits a total of 16 states deterin the TX and RX modes. For instance, a large powermined by four bias controls, Vc1–Vc4, as each biashandling capability is more critical for the TX modethan for the RX mode because the signal power levelcontrol has two input signals—below and above theapplied to the T/R switch from the TX can be as highdevice threshold voltage. As the topology featuresfour antenna ports, it allows afull range of switching statesand can support both a oneANT1A RXuplink–three-downlink andRRa two-uplink–two-downlinkGGRGRGantenna operation. However,Vc1 Vc1–Vc3–Vc3 the 4P4T T/R switch suffers larger insertion loss ascompared with the SPDTVrVrRGRGRGRGT/R switch because the signal needs to pass through anVc1–Vc1 Vc3 Vc3–additional transistor betweenA TXANT2ANT and TX/RX. Furthermore, both 4P4T and SPDTANT3B RXT/R switches show simiRGRGRGRGlar isolation because addedswitches are not helpful inVc2 Vc2–Vc4 Vc4–improving isolation.A brief comparison ofT/Rswitch topologies isRGRGVrRGVrRGsum marized i n Table 3.Vc2–Vc2 Vc4 Vc4–Our intention is to provideresearchers/designers someANT4B TXgeneral information on howto select an appropriate T/RFigure 5. Four-pole four-throw transmit/receive switch topology [31].switch topology.ANTM290February 2010

Device Circuit ModelsTABLE 3. Summary of T/R switch topologies.Bulk NMOSSystem CharacteristicsFigure 6(a) shows the cross-sectional viewof a typical bulk NMOS transistor. NoteTopologythere are two parasitic diodes between theSeriessubstrate and source and drain. The substrate is typically biased to 0 V. Thus, if noSeries-shuntdc bias (greater than 0 V) is applied, as theDifferentialsignal amplitude approaches 0.6 V, theseAsymmetricdiodes start to become forward biased andlimit the power-handling capability P1dBat about 6 dBm in a 50-V system. Figure 6(b) showsa small-signal circuit model for the ON state ofthe NMOS transistor [19], [32]. At low frequencies, theon-resistance Ron determines insertion loss. As theoperating frequency increases, insertion loss willincrease due to an increase of capacitive coupling ofthe signal through the ON-state parasitic capacitancesCdb, Csb, Cgd, Cgs, and Cgb to the substrate resistanceRB. Figure 6(c) shows a small-signal circuit modelfor the OFF state of the NMOS transistor [19], [32].Similarly, at low frequencies, the off-resistance Roffdetermines isolation. Roff is typically more than 100 kV,leading to very good isolation at low frequencies.However, at high frequencies, isolation deterioratesgreatly due to OFF-state parasitic capacitances Cdb,Csb, Cgd, Cgs, and Cgb and channel capacitance cellentGoodExcellentPoorGoodGoodExcellentthere are four parasitic diodes, i.e., P-well-source,P-well-drain, P-well-deep-N-well, and Psub-deep-Nwell [22]. The triple-well NMOS has better performance than bulk NMOS in terms of noise isolationand body bias control. For CMOS technology at nodesbelow 130 nm, the incremental cost of the triple-welloption is becoming insignificant. Hence, triple-wellNMOS has become a popular choice to improve designrobustness [26]. Figure 7(b) shows a small-signal circuit model for the ON state of the triple-well NMOStransistor. The on-state resistance Ron determines theinsertion loss. Figure 7(c) shows a small-signal circuitmodel for the OFF state of the triple-well NMOS transistor. Off-state capacitances Cdb, Csb, Cgd, Cgs, and Cdsdeteriorate isolation.Triple-Well NMOST/R Switch CircuitTechniques and ConceptsFigure 7(a) shows the cross-sectional view of a typicaltriple-well NMOS transistor, which consists of a P-wellembedded within a deep N-well to create an isolatedbody for the NMOS from the P-substrate (Psub). NoteCMOS T/R switches suffer from substrate loss due tothe low resistivity of the silicon substrate. The loading of parasitic diodes makes T/R switch design challenging when trying to achieve low insertion lossSRGGBDn SN-Wellp n p n RGGn DBSubstraten p n p p-Wellp-Type SubstrateDeep ruary 2010SCsbCdbCds(b)Figure 6. (a) Cross-sectional view of an NMOStransistor, (b) ON-state model, and (c) OFF-state modelwith the gate floated and the body grounded. (Figure in (b)taken from [19].)RGGCgdCgsSDCsbCdbCds(c)Figure 7. (a) Cross-sectional view of a triple-well NMOStransistor, (b) ON-state model and (c) OFF-state model withboth the gate and body floated. (Figure in (a) taken from [30].)91

Wm 5VcK 1K 2 5 1 12 Q 2s 2 3 2 1 12 Q 2s 2 1 3K 4 12Q 2s 1 3K1 4 2 6,Å Z 20 5 1 2K 1 3 2 3 2 1 1 2 Q 2s 2 1 3K 4 1 3Qs 1 3K 1 4 2 6RGPort 1(1)MPort 2CLFigure 8. Switch design using bulk NMOS and LC-tunedbody-floating technique [24].and high P1dB. To address this problem, several circuittechniques and concepts have been developed recentlythat have greatly improved the performance of CMOST/R switches for P1dB 11–30 dBm, insertion loss 1.5–0.1 dB, and isolation 24–30 dB at 2.4 GHz [32], [33]. Forsimplicity, we have purposely used single-pole-singlethrow (SPST) topology in Figures 8–14 to illustrate thekey characteristics of various techniques.Optimizing Device DimensionsOptimizing device dimensions is a fundamental technique in designing any CMOS circuit. The size of aswitch transistor is optimized to obtain the minimuminsertion loss. To achieve lower insertion loss, one needsto reduce the on-resistance by enlarging the transistorgate width. However, a larger transistor gate widthwill lead to larger parasitic capacitance in the substrate, which results in more signal loss in the substrateas well as degradation of isolation. Furthermore, thisphenomenon is magnified as the frequency increases.Therefore, the trade-off between the on-resistance andparasitic capacitance yields an optimum value for thetransistor gate width at a given frequency. Yamamotoet al. derived the optimum value [32] asVcRGPort 1MPort 2RFigure 9. Switch design using triple-well NMOS andresistive body floating.92where K1 and K2 are constants and K K1/K2; Qs 1/vCsRs; Rs and Cs represent parasitic resistances and capacitances resulting from a low-resistivity substrate. Itshould be mentioned that on-chip inductance can beused to tune out parasitic capacitance so that a largertransistor width can be allowed [34]. Furthermore, thecustomized layout with asymmetric drain and sourcemay be used [35]. The customized layout increases thedistance between the drain and source by stretching oneside. As a result, only the drain or the source area is enlarged. The distance between them is fixed at four timesthe p-cell default, which is to ensure the minimizeddrain-source coupling due to metal interconnections.This reduction of drain-source coupling will improveboth insertion loss and isolation performance.Minimizing or Maximizing Substrate ResistancesThe substrate resistance RB increases insertion lossmore at higher frequencies. Huang and O studied thedependence of insertion loss on the substrate resistance and parasitic capacitances and found there is avalue of substrate resistance, RB(MAX), for which insertion loss is maximum [19]RB1MAX2 52 v 2C 2T 1 RON Z0 1 Z 20 22v 2C 2T 1 RON 1 2Z0 21"v 4C4T 1 RONZ0 1 Z20 2 2 1 4v 2C2T 1 RON 1 2Z0 2 2,2v 2C2T 1 RON 1 2Z0 2(2)where Z0 is the characteristic impedance and CT 5CDB 1 CSB 1 3 1 CGD 1 CGS 2 CGB / 1 CGD 1 CGS 1 CGB 2 4 . As aresult, one needs to either minimize or maximize thesubstrate resistance to avoid the value of RB(MAX) inorder to achieve low insertion loss in CMOS bulk T/Rswitches. This can be done by reducing RB to near zeroor increasing RB to a very large value. The small RB canbe achieved by fully surrounding the transistors withlarge area P1 substrate contacts and filling in any openspaces with substrate contacts [19]. The large RB can berealized by blocking the P implants close to the switchNMOS transistors and placing the substrate connections far from them [25], [36].Body-FloatingBody-floating is probably the most important circuittechnique that improves all the performance parameters of CMOS T/R switches. Talwalkar et al. reportedthe LC-tuned body-floating technique for bulk NMOSin [24]. As shown in Figure 8, by using an on-chipFebruary 2010

inductor and capacitor, one can tune the bulk of theswitching transistor to be floating at certain frequencies.This technique, however, increases the design complexity and consumes large silicon area. Furthermore, theeffect of internal capacitive loss cannot be reduced.The resistive body-floating technique is not viablewith bulk NMOS because it involves manipulationto the substrate conditions. Taking advantage of themodern triple-well CMOS process, Yeh et al. realized the resistive body floating simply by using alarge resistor to bias the bulk as shown in Figure 9[33]. As resistors are intrinsically wideband, the P1dBimprovement is also wideband. The area is saved ascompared with the LC-tuned approach; however, thelinearity improvement to 21 dBm is not comparableto the LC-tuned technique [24], where more than28 dBm was achieved.Li and Zhang introduced the double-well bodyfloating technique in [22] to overcome the resistive bodyfloating limitation presented previously. As shown inFigure 10, in addition to both the P-well and deep-N-wellbiased through large resistors to make them RF floating,the deep-N-well should also be floated. With both terminals floated, the P-well-deep-N-well diode is then madesafe. In a similar manner, the Psub- deep-N-well diode isthen unprotected and may be turned on by large signals.However, as the bootstrapped effect is digressive, the signals that can turn on this diode need to be very high.The switched body floating technique is presentedin [35]. As shown in Figure 11, the body floating is controlled by an additional switch, S, connected in parallelwith the biasing transistor to provide controllable impedance between the body and its dc-biasing voltage. Whenthe switch transistor, M, is turned ON, its body switchtransistor, e.g., S, is turned OFF. The body of the ONswitch transistor becomes RF floating, and vice versa.Consequently, the body of the OFF switch transistorbecomes RF grounded, and the drain-source couplingthrough the body is significantly reduced [35]. A drawback of the switched body floating technique is that theinsertion loss is degraded. This is due to extra loss causedby the parasitic to the body when the OFF switch transistor is RF grounded. Naturally, the insertion loss of a T/Rswitch with switched body floating technique is inferiorto that of T/R switch with its body always floating.VcRGPort 1MPort 2R2VbR1Figure 10. Switch design using triple-well NMOS anddouble-well body floating.VcRGPort 1MPort 2SR2R1VcVbFigure 11. Switch design using triple-well NMOS andswitched body floating.to ground at each successive drain/source node [37].The asymmetry produces an unequal splitting of theRF voltage causing the transistor nearest to the signalsource to experience the largest voltage and breakdownfirst. Again, the concern is unwarranted with triple-wellNMOS as the body is floated at RF and isolated fromthe substrate. Increasing the number of stacked transistors effectively improves the power handling and isolation, while compromising the insertion loss. Therefore,it is expected that there exists an optimum number ofstacked transistors for which the switch performance isoptimized, and the reasonable range for the number ofstacked transistor is from two to five.Transistor StackingThe stacked transistor technique, as shown in Figure 12, improves P1dB but degrades insertion loss.Ohnakado et al. proposed using depletion-layer-extended transistors and Poh and Zhang proposed usingtriple-well NMOS to compensate such a drawback [30],[37]–[39]. Triple-well NMOS, with the resistive bodyfloating technique can prevent losses through the body,thereby facilitating an equal voltage division, as wellas manageable insertion loss. It was highlighted thatthe stacked transistors result in different impedanceFebruary 2010VcVcRG1RG2Port 1Port 2M1M2Figure 12. Switch design with stacked transistors.93

LPort 1Port 2C2C1MSummary and Further DevelopmentRGVcFigure 13. Switch design with stepped impedance concept.Stepped ImpedanceThe stepped impedance concept plays an importantrole in a T/R switch having an asymmetric topology.The stepped impedance concept is based on LC resonance [25], i.e., the impedance of an LC circuit becomeszero at the series resonance but is infinitely large at theparallel resonance. Figure 13 illustrates the implementation. When Vc is low, M is turned OFF and L-C2 formsa series resonator. On the other hand, when Vc is high,M1 is turned ON and L-C1 forms a parallel resonator.Obviously, the quality factor of L affects the performance and bandwidth of stepped impedance.Travelling WaveThere have been a few attempts to design T/R switchesin CMOS for millimeter-wave applications [40]–[43].The switch parasitics and voltage stress severelydegrade the switch performance at millimeter-wavefrequencies. The traveling-wave concept has beenadopted to guide the design [42]. As sh

Flipping the CMOS Switch. February 2010 87 generally consists of one transmission branch and one reception branch [1]. Along the recep-tion branch, the received RF signals will be passed through a bandpass filter (BPF) and then switch