Transcription

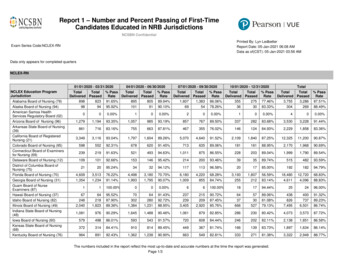

New Package/Board Materials Technology for Next-Generation Convergent MicrosystemsNitesh Kumbhat, P. Markondeya Raj*, Shubhra Bansal, Ravi Doraiswami, S. Bhattacharya and Rao TummalaPackaging Research CenterGeorgia Institute of TechnologyAtlanta GA 30332-0405Susan Hayes and Steve AtmurStarfire Systems, Inc.,10 Hermes Road, Malta NY.Phone: 404 894 2652* raj@ece.gatech.eduAbstractCurrent printed wiring boards (PWBs) are all organic,the most common being epoxy-glass laminate FR-4 due toits cost effectiveness and overall performance. However, forhigh-density wiring (HDW) and assembly of flip-chipsdirectly to the substrate without the use of underfill,substrate materials with low CTE and high elastic modulusare needed. Novel low CTE-high stiffness organic (carbonepoxy) and inorganic boards (carbon-SiC) have beenevaluated for flip-chip on board technology without the useof underfill. Standard liquid-liquid thermal shock tests werecarried out on test vehicles with different board materials.In-situ warpage measurements and optical microscopy wereused to analyze the observed failure modes.The low CTE low stiffness ceramic and organic boardsdid not fail from solder joint failure but from cracking in thedielectrics and copper wiring. The high stiffness ( 350 GPa)ceramic boards did not fail even after 1000 cycles. Thefailure modes indicate that a combination of high dielectricstresses and warpage results in crack propagation inconventional epoxies. The novel high stiffness low-CTEceramic (C-SiC) is also processable in large-area at low costand is hence a promising board material for futuremicrosystems.1. IntroductionThe system-on-a-package (SOP) design paradigmprovides a package level integration of digital, RF/analog,and opto-electronic functions. Two major components ofSOP are sequential build-up of multiple layers of conductingcopper patterns with interlayer dielectrics on a board andmultiple ICs flip-chipped on the top layer. A wide range ofpassives, wave-guides, and other RF and opto-electroniccomponents are buried within the dielectric layers [1]. Theinterleaved Cu and dielectric layers also support the highdensity interconnects for power and signal requirements.The board material should therefore meet certain electrical,thermo-mechanical reliability, HDI processing, and costrequirements.Reliability of a SOP assembly is affected by thethermomechanical stresses induced in the package due to theCTE mismatch between the die and substrate and the buildup materials. A silicon die has an approximate CTE of 2-Fax: 404 894 38423ppm/oC, while the conventional FR-4 substrate has a CTEof approximately 18-20 ppm/oC [1]. Though underfillmaterials are being used to enhance flip-chip reliability, theyimpose several bottlenecks to accomplish high componentdensity, fine pitch and unlimited I/O connections. Therefore,there is a pronounced need to evaluate board materials withCTE close to that of Si for reliable flip-chip on boardwithout underfill.The thermomechanical stresses due to CTE mismatch inthe system result in solder joint failure, die cracking anddelamination of the solder bumps and cracking of the buildup layers, leading to the failure of the assemblies. Stressmanagement, therefore, has been an essential aspect ofmicrosystems.This paper assesses the reliability of candidate basesubstrate materials in comparison to conventional FR-4boards. A novel large-area processable ceramic composite(C-SiC) board has been developed and evaluated for its flipchip reliability without underfill. The failure modes werestudied by optical microscopy and in-situ warpagemeasurements.2. ExperimentalC-SiC Board Manufacture: Composite panels of carbonfibers and a silicon carbide matrix are formed fromcommercially available carbon fiber fabrics and felts and aliquid polymeric ceramic precursor.The polymericprecursor is a highly branched polycarbosilane, whichdecomposes on firing to 850 C to give amorphous siliconcarbide. Hydrogen is the main byproduct of the pyrolysisand is diluted and vented to the outside.In a typicalpreparation, layers of felt or fabric are cut to the desired sizeand shape, soaked in either the polymer or a slurry ofpolymer and silicon carbide powder. Hot pressing usinglight pressure (60 - 300 psi) gives flat panels up to 10” x 10”square with porosities ranging from 20 to 50%. To improvestrength and stiffness, the panels are re-infiltrated with thepolycarbosilane and the pyrolysis repeated until the porosityis below 5% (8 to 10 cycles). Planarity is best maintained ifthe panels are held flat under light pressure (1 to 5 Psi)during these re-infiltration/pyrolysis cycles.To give the pore-free and planar surface required forwiring boards, the panels are lapped briefly and a paste

polycarbosilane/silicon carbide powder worked into thesurface.The panel is then pyrolyzed and given twopolymer infiltration/pyrolysis cycles to insure a pore-freesurface. The surface of the panels is finished with a lightlapping. The properties of fabricated panels are summarizedin Table 1.Fabrication of Test Vehicles: Test vehicles werefabricated using the sequential build-up process. Continuousunidirectional (Toray) and discontinuous carbon fiber (CCS)reinforced epoxy composites, FR-4, high stiffness ceramic(Cer2) and low stiffness ceramic composite (Cer1) wereused as the candidate base substrates for the test vehicle.FR-4 test vehicle was used as a standard for comparison.Carbon fibers have ultra low CTEs and high moduli, so theirreinforcement in polymers seems to be a promising solutionto get low CTE and moderate stiffness boards. These boardsare inexpensive, have easy machinability and large areaprocessability. To evaluate the increase in reliabilityperformance of boards with CTE close to that of silicon, testvehicles were fabricated both with and without underfill.The properties of candidate boards are summarized in Table2.Figure 1 shows the structure of test vehicle and processsteps during the fabrication. The fabrication was done onboards with dimensions varying from 10-12 cm, each side.The carbon-epoxy substrates were initially roughened byReactive Ion Etching for better polymer adhesion. Twodifferent thickness (10 and 25 microns) of epoxy (CIBA7081, Ciba-Geigy) layer were spin-coated on the substrate toprovide the first insulation layer. Electroless copper platingwas done using Shipley’s process and the copper wiring wassubsequently electroplated up to 12 microns. The ceramiccomposite test vehicles were fabricated with RCC (resincoated copper) lamination using Matsushita's (Koriyama,Japan) R0880 multilayered PCB materials. The RCC foilhas 60-70 microns thick dielectric.Base BoardSpin Coating ofDielectricMetallizationusing RCC andPatterningSolder MaskingChip AssemblyFigure 1: Flow chart for test vehicle fabrication.The final solder mask coating (25 microns) was donewith Taiyo solder mask (PSR 9000 A02 series) composition.Bumped PB-8 dies (Flip-Chip Technology, PracticalComponents, CA) were assembled on the board withconventional flip-chip process both with and withoutunderfill materials. A commercially available fast-flow,snap-cure underfill (Dexter 4531, Loctite Corporation) wasused.Reliability Test: The reliability was evaluated withliquid-liquid thermal shock tests. Test vehicles weresubjected to a thermal shock between -55oC to 125oC usingliquid media. The thermomechanical reliability of theelectrical interconnections was evaluated.Shadow Moiré in-situ Warpage Measurements: The insitu warpage measurements on the test vehicles during thethermal cycling were done at Akrometrix LLC., Atlanta,using the TherMoiré@ measurement system. This is anoptical, temperature-dependent measurement system basedon the Shadow Moiré technique, and includes automatedphase stepping analysis. This non-contact full fieldmeasurement method generates a Moiré pattern of light anddark regions produced by the superposition of two regularmotifs that geometrically interfere. A grating shadow, whichdistorts in the presence of surface warpage, is produced onthe specimen when a collimated light source is directedthrough the reference grating. The specimens weresupported with two parallel metal rods at each end to ensurefree expansion in all directions. A grating density of 100lines/inch with a resolution of 10 mils/fringe and a phasestepping sensitivity of 0.1 mils was used. The prescribedthermal cycle imitated the standard liquid-liquid thermalshock test (-55 oC to 125 oC but at a slower rate of 1oC/min.Test vehicle fabrication for the shadow-moiré and reliabilitymeasurements was exactly the same. Liquid nitrogen wasused to cool the samples to –55oC. All boards are ofdimensions 12 cm x 12 cm except for Toray board which is10 cm x 7.5 cm.3. Results and DiscussionC-SiC Fabrication: The main aim of this part of projectis to achieve very high modulus. There is a trade-offbetween high modulus and high flexural strength; as thecomposites are made stiffer they also become more brittle.Current work to increase stiffness without causingembrittlement includes optimizing the panel’s fiberarchitecture and using both higher modulus fibers andhigher slurry loadings. Future work in this direction is toexplore methods for obtaining the required low porositywith fewer re-infiltration cycles (currently 8 to 12 arerequired) and retaining greater planarity throughout theprocess so that less lapping is required to finish the plate.Reliability Test: Thermal shock tests for flip-chip onboard both with and without underfill were done on 5different boards with different CTEs and elastic moduli. Inorder to understand the failure mechanisms, failure modeanalysis was done using optical microscopy.Several types of failure modes namely solder jointcracking, solder joint delamination, dielectric cracking,underfill and die cracking have been observed in the testvehicles. Conventional base substrate material FR-4 hasbeen observed to fail within the first 100 cycles withoutunderfill. As expected, the failure occurred at the solderjoints due to the huge CTE mismatch between the Si die andthe board. Test vehicles with underfill have been observedto sustain up to 1800 cycles as the underfill redistributes thestresses in the solder joints. Test vehicles built on low CTE

substrates with low modulus ( 100 GPa) also fail at earlystages of thermal cycle, both with and without underfill, themode of failure in this case predominantly being dielectriccracking. For organic boards, solder joint cracking was alsoobserved. The low CTE of board results in a high CTEmismatch between the dielectric and board which generateshigh stresses in the dielectric causing it to crack. In addition,the low stiffness causes the boards to warp during thermalcycling leading to solder joint delamination. The cracks inthe dielectric propagate into the copper lines breaking theelectrical continuity and thereby leading to failure of theassembly as shown in Figure 2. It can be noticed that for thecarbon cloth reinforced epoxy substrate (CCS), reliability isquite low though effective CTE mismatch between the dieand the board has been eliminated.The unidirectional carbon - epoxy boards (Toray) with ahigher modulus ( 180 GPa) show similar failure modesthough they fail at a later stage than board A, both with andwithout underfill.The stiffer ceramic board which is a low CTE-highstiffness (350 GPa) board has good reliability both with andwithout underfill and does not crack even after 1800 cyclesas evident from Figure 4. It was also seen that the boardswith lower thickness of dielectric did not show any crackingafter 1800 cycles while boards with thicker dielectriccracking showed small cracks at solder mask corners after500 cycles. The thermomechanical reliability test results andfailure modes are summarized in Table 3.CrackFigure 3: Failure modess in low stiffness ceramic boards.Figure 2: Failure modes in carbon-epoxy boards.The ceramic composite board (cer1) did not show anyfailure in the solder joints even after 500 cycles because ofits close CTE with that of Si. The flip chip daisy chain iscompletely connected though some of the pads showed highresistance implying that the failure was within the lines andnot in the solder joint connected through the daisy chain.The warpage in these boards is lower compared to theorganic boards because of its stable mechanical propertiesand absence of glass-transition temperature seen in epoxyboards. However, severe dielectric cracking is observed atthe corners of the solder mask openings near the testing padsand along the edges of the solder mask openings. Thesecracks were also seen to penetrate through the copper lines.Cracks within the copper lines, independent of dielectriccracking were also observed within the solder maskopenings as depicted in Figure 3.Shadow Moiré Measurements: To further analyze thesefailure mechanisms, in-situ warpage was measured tomonitor the board behavior during thermal cycling. CCSCarbon boards, which have a low stiffness, warp mostduring thermal cycling showing an out of planedisplacement of as high as 27 µm/inch board. On the otherhand, high stiffness ceramic board (Cer2) shows negligiblewarpage of about 3-4µm/ inch board. Conventional basesubstrate material, FR-4, also shows considerable warpageranging from 7-12 µm/inch board over the cycledtemperatures (-55 to 125) C. The experimental results areshown in Figure 5.The ceramic composite board with 80 GPa stiffnessshowed a warpage going from a minimum of 6.5 µm/inchat 100 C to 13 µm/inch at -55 C. The Toray boards whencycled from 27 C to 125 C showed a warpage ranging from6 to 1 µm/inch. These numbers are correspondingly lowercompared to that of CCS boards. In the ceramic compositeboard Cer1, dielectric cracks were only seen at the cornersand interfaces, which presumably are stress concentrationregions. The large dielectric cracks which cut through thecopper lines in CCS boards were not observed here.

failure. Hence, it can be inferred that a combination ofwarpage and dielectric stresses initiate these failures.Conventional brittle epoxies with low elongation to failure(low toughness) low strength, high CTE mismatch and highstiffness may not be the right candidate dielectrics for theseboards. Dielectrics which lead to lower stress and havehigher strength and toughness are required. Table 4compiles the mechanical properties for some candidate SOPdielectric materials. While the electrical properties dictatethat low loss dielectrics like BCB are needed for chanical properties also need to be considered forproper selection of the dielectric materials.Figure 4: No cracks observed in high stiffness ceramicboards with 10 µm epoxy and solder mask build-up.Figure 5: In-situ warpage measurements. Cer1: Lowstiffness ceramic; Cer2: High stiffness ceramic.Analytical models predict similar dielectric stresses forall the low CTE boards with CTE ranging from 1-5 ppm/C[2]. The dielectric cracking phenomena is insignificant inthe high stiffness ceramic boards while the cracks in the lowstiffness boards are more severe and lead to electrical4. ConclusionsThis paper evaluates low CTE organic and inorganicboard materials with a range of stiffness for reliability withand without underfill. While the solder joint stresses can beeliminated with boards having Si-matched CTE, thedielectric stresses and warpage result in the failure in thesetest vehicles. Hence, in-situ warpage of different boards wascharacterized with shadow-moiré technique and is correlatedwith the observed failure phenomena.The results show that the failure in the flip chip testvehicles originate from cracks within the dielectric andcopper lines, and the cracking corresponds to the measuredwarpages during thermal cycling.The high stiffness ceramic boards did not fail after thethermal shock test. These ceramic boards can bemanufactured in large-area using a low-cost processingtechnique and is hence an ideal candidate material for futureSOP substrates.Acknowledgements:This project is funded through the NIST-ATP and NSF(grant number EEC-9402723).References1. Tummala, R et al., “High density packaging for 2010and beyond”, Proc. 4th International Symposium forElectronic Materials and Packaging, Taiwan, 2002, pp.1-10.2. Hedge, S., et al., “Enhanced Reliability of HighDensity Wiring (HDW) Substrates through NewDielectric and Base Substrate Materials”, Proceedingsof IMEC, 2002, pp. .Table 1: Properties of the fabricated ceramic matrix composites.PropertyCurrent board propertiesSet 1Set 2Project GoalThicknessCTEModulus2 mmNA190 GPa2 mm3.0 ppm/ C100 GPa1 to 0.5 mm2 - 4 ppm/ C 350 GPaFlexure strengthPlanarityPanel Size (finished)50 MPa /- 50 microns5” x 5”300 MPa /- 50 microns5” x 5”Panel cannot be brittle /- 5 microns18” x 24”

Table 2: Constituents and properties of boards.Candidate SubstrateClothClothFillerorContentshort fiber(Vol Short Fiber48522.9100None604000.5180High Stiffness Ceramic*(Cer 2)****4350Low Stiffness Ceramic*(Cer 1)****380Carbon Short Fiber/NoneEpoxy Resin (CCS)UniUniDir.Dir. Fiber 0 /90 /EpoxyFiberResin (Toray)0 /90 47Matrix (Vol %)PropertiesCTEModulus(ppm/ C) (GPa)Table 3: Reliability Test Results.SubstrateCTE(ppm/oC)Modulus(GPa)Failure MechanismsUnderfillCyclesfailureFR-41618.2Solder Joint CrackingCCS5100Toray0.5180Dielectric cracking; Solderjoint delaminationDielectric CrackingHigh stiffnessceramic (Cer 2)Low stiffnessceramic (Cer 1)4350-2-380Dielectric Cracking; Copperline cracking and cracksalong solder mask 0018001800400500Table 4: Mechanical properties for some candidate SOP dielectric materials.MaterialEpoxyBCBAvatrelSiloxaneCTE, ppm/C6045-508355Mod. GPa3.52.512.5Strength; Failure to elongation30-83 MPa; 2-10 %;87 MPa % ; 8 %50-60 MPa; 20 %;Low CTE Polyimide106-9200-390 MPa; 15-34 % ;for

Though underfill materials are being used to enhance flip-chip reliability, they impose several bottlenecks to accomplish high component density, fine pitch and unlimited I/O connections. Therefore, there is a pronounced need to evaluate board materials with CTE close to that of Si for reliable flip-chip on board without underfill.